오늘날 컴퓨터 시스템, 프로세서, I/O 디바이스는 메모리 시스템의 데이터에 액세스 하기 위해 하나이상의 메모리 컨트롤러를 거친다. 메모리 컨트롤러는 DRAM디바이스에서의 데이터 이동을 관리하는 동시에 프로토콜을 준수하며, DRAM디바이스 고유의 전기적 특성, 타이밍 특성을 책임지고 심지어 특정 시스템에서는 에러의 검출과 수정까지 담당한다.

DRAM 메모리 컨트롤러의 설계와 구현은 DRAM 메모리 시스템의 Bandwidth, Access latency에 영향을 미친다.

13.1 DRAM 컨트롤러 아키텍쳐

Instruction set architecture처럼 프로세서의 프로그래밍 모델을 정의하는 것 처럼, DRAM 액세스 프로토콜은 DRAM 메모리 컨트롤러와 DRAM 디바이스의 시스템 사이의 인터페이스 프로토콜을 정의한다. 동일한 ISA를 지원하는 프로세서라 하더라도, 각각의 마이크로 아키텍처 구현에 따라 완전히 다른 성능을 가질 수 있다. 이처럼 동일한 DRAM 액세스 프로토콜을 지원하더라도 각각의 마이크로 아키텍처 구현에 따라 성능이 의존한다.

최소 다이사이즈, 최소 파워 소모량, 최대 시스템 성능을 가지거나 혹은 상충되는 목표들이 최적화되는 타협안으로 설계될 수 있다. 특히 Row-Buffer-Management Policy, the Address Mapping Scheme, and the Memory Transaction and DRAM Command Ordering Scheme 은 DRAM 메모리 컨트롤러를 설계하고 구현하는데 있어서 중요하다.

이 장에서는 추상적인 DRAM 메모리 컨트롤러 설계의 기본적인 개념에 대하여 다루고, 특정한 주제의 경우 기존의 연구를 인용한다.

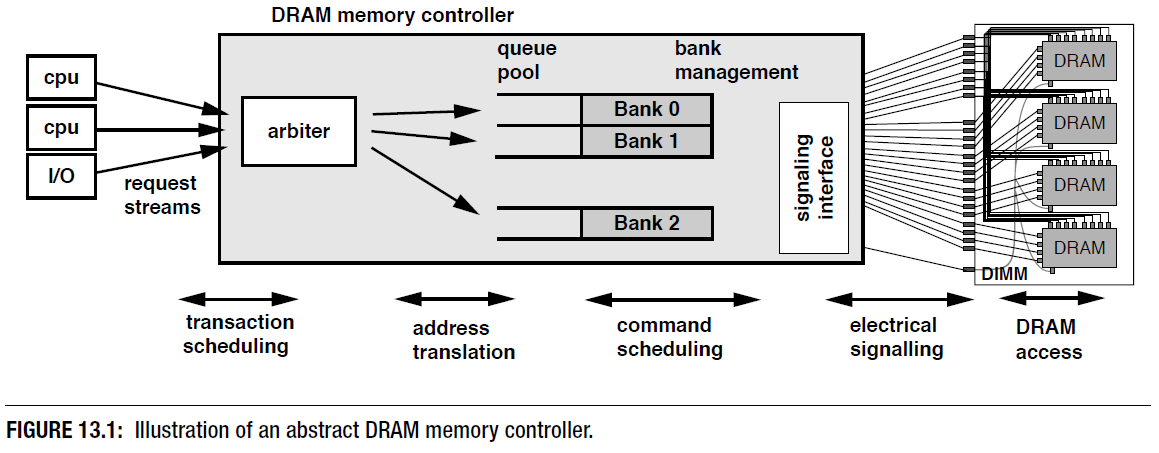

Figure 13.1은 추상적인 DRAM 메모리 컨트롤러의 기본 컴포넌트를 나타낸다. 하나 이상의 마이크로프로세서들과 I/O 디바이스들로부터 Request 를 받고 어떤 Request를 메모리 컨트롤러로 배치할지 결정하는 중재 인터페이스를 제공한다.

위의 그림은 하나의 Transaction이 결정되고 나서 메모리 컨트롤러로 들어가면, 메모리 어드레스 위치에 쓰여지고 DRAM Command Sequence로 변환되는 것을 보여준다. Command sequence는 메모리 컨트롤러 내부의 Queue에 위치하게 된다. Command sequence는 컨트롤러가 실행 여부를 결정하는 일반 Queue pool로 배정되거나, 메모리의 랭크당 하나 혹은 뱅크당 하나 존재하는 Queue로 배정될 수 있다. 그 후에는 DRAM command scheduling policy에 의해서 command가 전기 시그널링을 통해 DRAM 디바이스로 스케쥴링된다.

13.2 로우 버퍼 관리 방침

오늘날 DRAM 디바이스는 sense amplifier 어레이를 임시 데이터 스토리지 역할을 하는 버퍼로 사용할 수 있다. 이번 장에서는 Row-Buffer-Management Policy로 불리는 sense amplifier 동작 관리 방침을 알아본다. Open-page, Close-page 두가지가 존재한다.

13.2.1 오픈 페이지 로우 버퍼 관리 방침

상용 DRAM 디바이스 경우 DRAM 스토리지 셀로 데이터를 액세스 하기 위해서는 Row activation command와 Column access command의 2단계 프로세스를 진행해야한다.

Temporal, Spatial 상으로 유사한 메모리 액세스를 동일한 Row에 배치하는 방식으로 locality의 이점을 가져갈 수있다. Open-page Policy는 sense amplifier를 계속해서 Open하고 Access에 대비하여 데이터의 Row를 유지하는 것을 통해 메모리 액세스가 메모리의 같은 Row로 접근하는 것을 선호하도록 설계되었다.

즉 데이터 로우가 DRAM 셀의 뱅크에있는 sense amplifier 어레이으로 이동하면, 동일한 Row에 대한 다른 Column Access가 최소 latency인 tCAS만에 가능하게 된다. 그러나 같은 Bank의 다른 Row로 액세스 하는 경우에는 메모리 컨트롤러가 DRAM 어레이를 Precharge 한 후 새로운 Row Activation을 수행하고 Column Access를 수행해야 한다.

13.2.2 클로즈 페이지 로우 버퍼 관리 방침

Open-page 와 다르게 Random Address에 접근하거나 locality가 없는 데이터에 접근할 경우 최적화 되어있다. Open-page 방침 또는 그와 유사한 여러 방침들은 프로세서가 작은 범용 컴퓨터들을 위한 메모리 시스템에 사용된다. 반대로 Close-page 방침은 일반적으로 다수의 프로세서를 사용하는 멀티 프로세서시스템이나 특수 목적 메모리 시스템에 사용된다. 즉 이는 다수의 스레디된 Context의 메모리 요청이 Sequence가 감소되기 때문이다.

13.2.3 하이브리드(동적) 로우 버퍼 관리 방침

오늘날 DRAM 메모리 컨트롤러는 두 방침의 적절한 조합을 사용한다. Request 속도나 Access locality 등을 고려하여 최적화된 로우 버퍼 관리 방침을 정하는데 도움을 준다. 동적으로 변하기 위해서 DRAM 메모리 컨트롤러가 액세스 기록과 타이머를 모두 활용하여 로우 버퍼 관리 방침을 유동적으로 조정하여 성능 최적화와 파워 소모의 최소화하도록 해야한다.

Bank Conflict이 빠르게 연속해서 발생하여 로우 버퍼의 선택 회수에 해당하는 메모리 Read요청이 비율이 미리정해놓은 임계점 아래로 내려가면, DRAM 컨트롤러가 Close-page 방침으로 변환한다. 반대로 주어진 뱅크의 동일한 row에 계속해서 연속적인 Request가 들어오면 DRAM 컨트롤러가 Open-page 방침으로 변환한다.

또다른 방법으로 sense amplifier를 제어하는 타이머를 사용하는 방법이 있다. Row가 Activate되면 타이머를 미리 정해놓은 값으로 적어놓는다. 타이머는 매 클럭마다 카운트다운을 하게되며, 끝나면 해당 Bank를 Precharge하게 된다. 만약 중간에 Row buffe가 선택되는 경우에는 카운터가 초기화되어 처음부터 시작하게된다.

13.2.3 로우 버퍼 관리 방침에 따른 성능 효과

현재 Idle system경우, Close-page 의 read latency는 tRCD+tCAS이다. Open-page의 경우 최소 tCAS에서 최대 tRP+tRCD+tCAS 값을 가진다. tCAS는 로우 버퍼 선택 latency이고, tRP+tRCD+tCAS는 Bank Conflict Latency이다.

Open-Row buffer를 선택하는 메모리 액세스의 퍼센테지를 x라고 한다면 1-x는 Bank conflict의 퍼센테지이다. Open-page 시스템에서의 DRAM Access 평균값은 x*(tCAS) + (1-x)*(tRP+tRCD+tCAS)로 나타낼수 있다. 이 수식의 결과와 Close-page의 tRCD+tCAS를 이용하면 성능을 계산 할 수 있다.

13.2.4 로우 버퍼 관리 방침에 따른 파워 효과

로우 버퍼 관리 방침을 결정하기 위한 두번째 요소는 DRAM의 파워 소모이다. 예를들어 Table 13.1은 RDRAM메모리 시스템의 동작 전류 등급을 보여주고있다. DRAM Bank와 Activation 상태를 유지하는 DRAM 디바이스를 계속해서 대기 모드로 유지하는 것은 일정이상의 전류를 소모시킨다. 이는 DRAM 디바이스의 동작 모드에서 파워 소모 특성은 파워 소모를 최소화 하기위한 최적의 로우 버퍼 관리 방침을 정하기 위해서 메모리 요청 속도도 고려해야한다는 사실을 아렬준다.

'책 > 메모리 시스템' 카테고리의 다른 글

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-4' (0) | 2021.10.28 |

|---|---|

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-3' (0) | 2021.10.28 |

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-1' (1) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-4' (0) | 2021.10.28 |