12.2.4 EDO와 BEDO디바이스

1990년 중반 EDO(Extended Data-Out)가 소개되어 개인용 컴퓨터의 주류 메모리였던 FPM DRAM을 대체하기 시작했다. 새로운 OE/(Output Enable)신호를 추가하고, 출력 버퍼 제어를 CAS/신호에서 OE/신호로 대체하였다. 결론적으로 DRAM 디바이스의 출력에 Read된 데이터는 CAS/신호가 높게된 이후에도 Extended Data-Out이 라는 이름으로 남아 있을수 있다.

그림 12.8은 EDO 디바이스의 세 번의 칼럼 read 커맨드들의 타이밍을 나타낸다. 출력 데이터에 대한 정확한 출력은 CAS/ 데이터 홀드 타임에 영향없이 CAS/신호가 더 빨리 연속적으로 생성될 수 있는 것을 보여준다. 따라서 EDO 디바이스는 더 빠른 페이지 모드 사이클 타임을 달성 할 수 있다.

BEDO(Burst Extended Data-Out)디바이스는 EDO를 기반으로 활성화된 로우에서 새로운 칼럼 어드레스가 DRAM으로 전송될 때마다 데이터를 버스팅(Bursting)하는 개념을 추가하였다. 그림12.9는 RAS/신호가 low되며, BEDO디바이스에 로우 활성화 커맨드가 들어가는것을 보여준다. 칼럼 액세스 커맨드는 CAS/신호를 low로 만들고 칼럼 액세스 커맨드의 어드레스를 래치한다. 또한 네개의 연속적인 칼럼 어드레스들을 만들고, CAS/신호의 각 하강 에지마다 그 어드레스상의 데이터를 데이터 버스에 싣는다.

12.3 현대의 범용 DRAM 디바이스

DRAM디바이스가 더많은 기능을 가지고, 더 빠른 대역폭을 가지기 위한 요소들이 수렴되면서, DRAM 제조사들과 시스템 제조사들이 함께 JEDEC(Joint Electron Device Enginnering Council)을 수립하여 새로운 SDRAM이라는 DRAM디바이스를 정의했다.

SDRAM은 이후 디바이스들의 기초가되었다. DDR, DDR2, DDR3등의 SDRAM은 모두 SDRAM 이후의 세대이다. 또한 직간접적으로 GDDR, GDDR2, ESDRAM, VCDRAM, Mobile SDRAM등 다양한 디바이스들이 이후 세대임을 주장한다.

12.3.1 SDRAM

SDRAM은 이전세데의 디바이스와는 다음과 같은 세가지의 큰 차이점이 있다. SDRAM 디바이스는 동기화 디바이스 인터페이스를 가지며, 여러 내부 뱅크를 가지고, 프로그램이 가능하다.

첫번째, FPM, EDO 디바이스들에서 메모리 컨트롤러는 RAS/와 CAS/신호를 통해 DRAM디바이스 내부의 래치를 직접 조절했고, 이 신호는 DRAM디바이스에 언제든지 입력될 수 있었다. SDRAM 디바이스경우 커맨드 버스에서 커맨드 신호를 전달하기 위해 RAS/, CAS/신호의 이름은 남아 있지만, 더이상 디바이스의 래치를 직접 제어하지 않는다. 대신 커맨드 버스에 커맨드 신호들을 전달하면, 클럭 신호의 하강에지에서 커맨드로서 SDRAM디바이스의 컨트롤 로직에 의해 작동한다.

두번째, SDRAM디바이스는 내부적으로 다수의 뱅크를 가지고 있다. 독립적인 여러 뱅크가 존재함으로 하나의 뱅크가 로우 활성화 커맨드나 프리차지 커맨드로 Busy한 중에도, 메모리 컨트롤러가 다른 뱅크의 로우를 활성화시키기위해 로우 액세스 커맨드를 보내거나 칼럼 액세스 커맨드를 볼수 있음을 의미한다. 멀티 뱅크 아키텍처는 하나의 SDRAM 디바이스에서 파이프라인되어 여러 명령을 처리할 수 있음을 의미한다.

그림 12.10은 SDRAM의 블록 다이어그램을 나타낸다. PFM과 달리 4개의 뱅크를 가지고 각각 Sense amplifer를 가지고 있음을 보여준다. 데이터 흐름을 관장하는 어드레스 레지스터를 가지고있다.

로우 액세스 커맨드의 경우, 어드레스 레지스터의 어드레스가 로우 어드레스 래치와 디코더로 전달되고, 선택된 워드라인을 활성화 시키는데 사용된다. 데이터는 비트라인으로 전달되고, Sense amplifer는 전압차이를 감지하고 칼럼 액세스를 위해 데이터를 유지한다.

칼럼 Read 커맨드 경우 데이터는 여러 레벨들의 멀티플렉서로 보내지고, 이후 I/O 게이팅 구조를 통해 데이터 버스로 신호를 출력하고, 메모리 컨트롤러로 전달된다.

칼럼 Write 커맨드 경우 메모리 컨트롤러가 데이터를 데이터 버스에 놓고, SDRAM디바이스가 레지스터 안에있는 데이터를 래치하고, Sense amplifer 어레이에 있는 데이터로 덮어 쓰기한다. 이후 오픈 액세스 트랜지스터를 통해 DRAM셀들에 새로운 데이터를 넣는다.

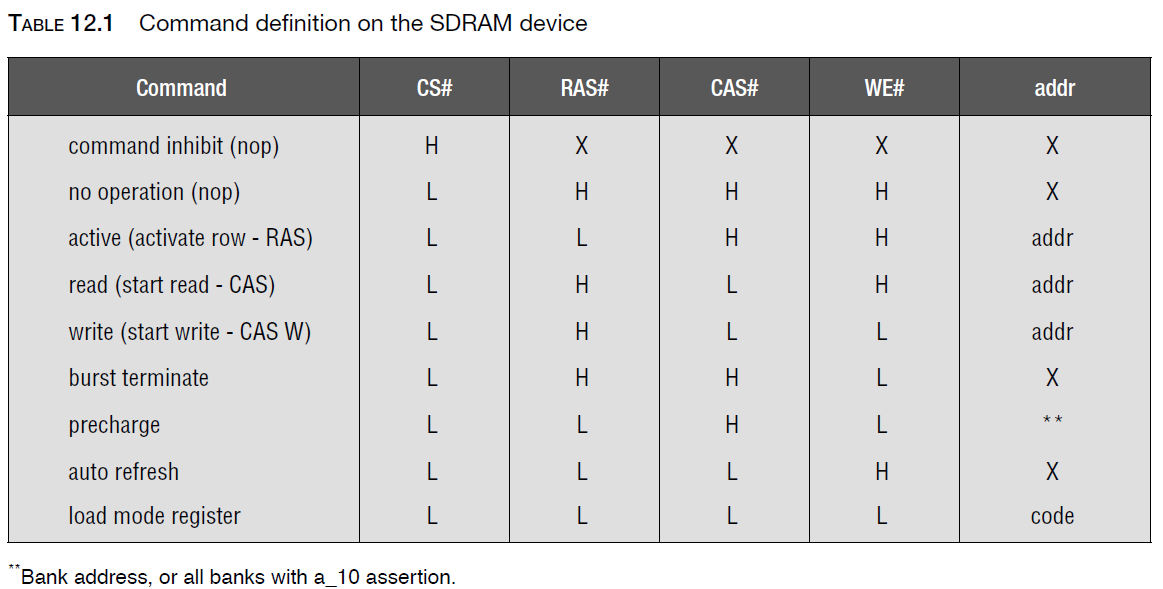

SDRAM 안에서 CS/(Chip Select Line)이 활성화되어있다면, 클럭 신호(CLK)의 상승 에지에서 커맨드들은 디코드된다. DRAM컨트롤러는 WE/(Write Enable), CAS/(Column Access), RAS/(Row Access)로 구성된 커맨드 버스들을 통해 커맨드를 전달한다. 표 12.1은 SDRAM디바이스 커맨드 세트와 커맨드 버스 신호의 조합들을 보여준다.

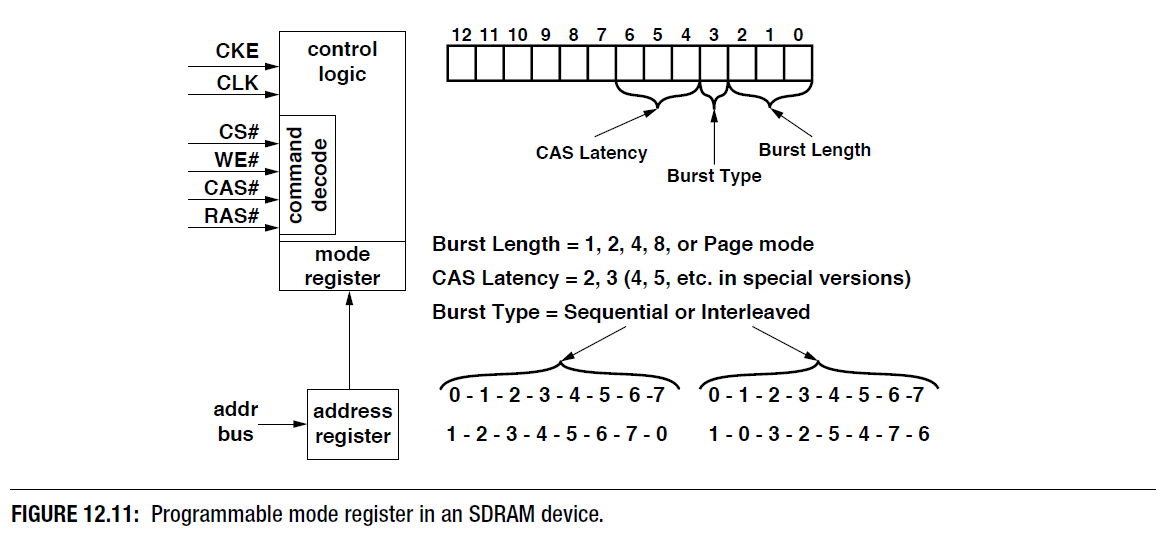

세번째, SDRAM은 프로그램 가능한 모드 레지스터를 가지고있고, 디바이스 동작이 모드 레지스터의 값에 따라 달라질 수 있다. 즉 해당 레지스터로 인해 커맨드에 대해 다른 동작을 할 수 있다. 특히 CAS/ Latency와 버스트 길이, 버스트 오더를 조절할 수 있다.

그림 12.11은 3개의 필드를 가지고있는 모드 레지스터를 나타낸다. CAS/ latency, Burst type, Burst length 가 있다. CAS/ latency 값에 따라서 DRAM디바이스는 칼럼 read 커맨드로부터 둘 또는 세 사이클 뒤에 데이터를 전송한다. 버스트 타입 값은 데이터를 전송하는 순서를 결정하고, 버스트 길이 필드는 한번의 칼럼 Read 커맨드로 메모리 컨트롤러에게 전달할 칼럼수를 결정한다.

'책 > 메모리 시스템' 카테고리의 다른 글

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-4' (0) | 2021.10.28 |

|---|---|

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-3' (0) | 2021.10.28 |

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-1' (1) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-4' (0) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-3' (0) | 2021.10.28 |