첫번째 DRAM 디바이스는 IBM에 의해 1966년에 발명되었다, 이후 Intel은 1970년 1103으로 불리는 상용 DRAM 디바이스를 출시했다. 이후 수십년간 DRAM 디바이스 아키텍처는 지속적, 점진적으로 변화해 왔다. 최근 몇 년간 메모리시스템에 대한 다양한 요구조건들은 DRAM 디바이스에 급격한 발전을 가져왔다. 이번장에서는 여러 DRAM 디바이스들의 원리와 기능에 대해 설명한다.

12.1 DRAM 디바이스 패밀리들

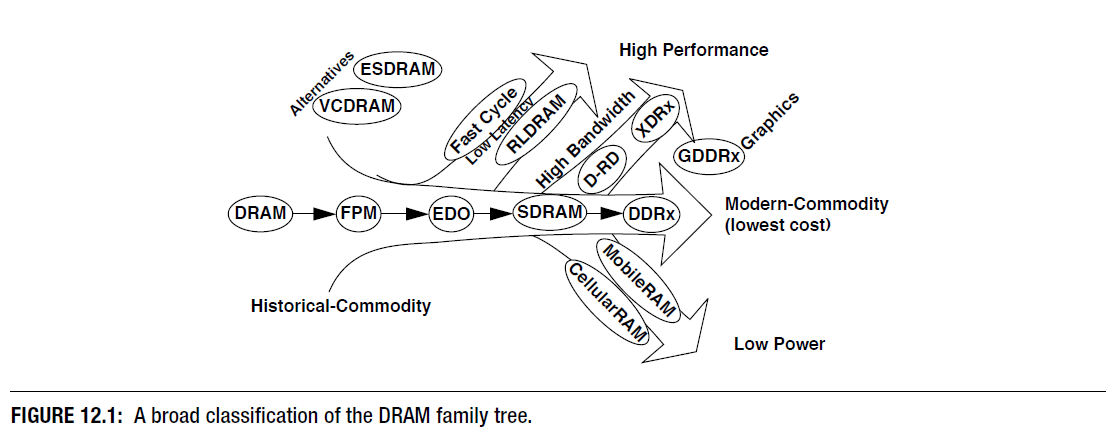

기본적인 charge-storage DRAM 회로가 발명되고 수십년간 조금씩 다른 구조를 가진 많은 DRAM 디바이스들이 낮은 가격, 높은 대역폭, 낮은 레이턴시, 낮은 파워 소모와 이들이 조합된 특정한 조건을 만족하기위해 개발되어왔다.

12.1.1 가격(용량), Latency, 대역폭, 파워소모

여러 DRAM 디바이스에 대해 설명하고, 비교하기위해 네가지 요소로 모든 DRAM 디바이스를 평가하고 네가지 경로로 DRAM 디바이스를 분류한다.

그림 12.1은 DRAM 디바이스들을 패밀리 트리상에서 네가지 진화 경로로 분류한다. 상용 경로, Low-Latency 경로, 고대역폭 경로, 낮은 파워 소모 경로이다.

12.2 초기의 상용 DRAM 디바이스

DRAM 디바이스들의 개발을 촉지한 가장 큰 요소는 저장 비트당 가격이다. 비용에 초점을 맞춘 결과 SDRAM출현 이전의 모든 DRAM디바이스는 '초기의 사용 제품'으로 분류한다. Intell 1103 DRAM, 비동기 DRAM, FPM DRAM, EDO DRAM, BEDO DRAM 등의 디바이스를 소개한다.

12.2.1 Intel 1103

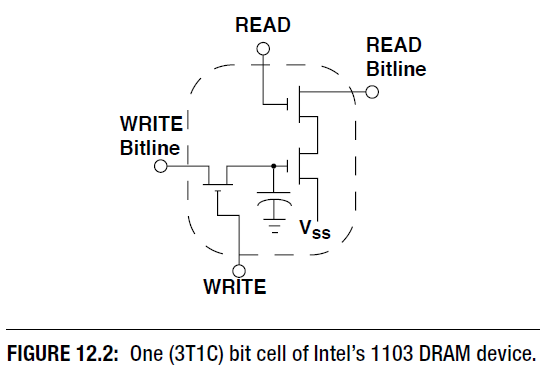

상대적으로 낮은 비용으로 인해 1103은 폭넓게 수용되고, 마그네틱 코어 메모리를 빠르게 대체했다. 580ns의 로우 사이클 타임, 300ns의 랜덤 액세스 타임을 가지고 있었다. 또한 2ms이상으로 보장된 데이터 보유시간을 가지고 있다. 1103은 단방향 데이터 입출력과 출력이라는 특징을 가지고있다.

단방향 입출력은 1103까지 초기 DRAM 디바이스들에서 Atomic read-modify-write 사이클이라는 흥미로운 기능을 제공한다. DRAM이 데이터를 출력하는 중에 메모리 컨트롤러가 어드레스 버스상의 어드레스를 홀딩할 수 있다. 또한 컨트롤러는 Read, Write를 같은 어드레스에 대해 동시에 할 수 있다. Row, Column 어드레스를 위해서 지정된 핀을 사용하는데, 이후 디바이스들은 해당 어드레스를 합해 멀티플렉싱한 어드레스 핀을 사용한다.

3T1C 구조를 기본 셀로 사용하여 Read-out한 데이터는 파괴되지 않는다. 다른 DRAM과 비교하여 1103은 가장 기본적인 어드레스 디코더를 가지고 있었고, 1024개의 DRAM 셀 어레이를 가지고 있었다. 대신 Integreated address, Latch Sense amplifer는 1103에 없었다. 결론적으로 이후 디바이스보다 더많은 외부회로가 필요했다.

1. TTL 디바이스와 MOS 신호간 인터페이스를 위해 외부전압레벨 시프터가 필요하다.

2. Read, Write 동작을 위해 많은 외부 로직이 필요하다.

3. 메모리로 부터 값을 읽어내기 위해 외부 Sense amplifier가 필요하다.

12.2.2 비동기 DRAM 디바이스

1970년대 중반까지 DRAM디바이스 인터페이스는 Clock-driven 인터페이스와는 거리가 멀었고, 주로 비동기 커맨드-데이터 타이밍 인터페이스를 사용했다.

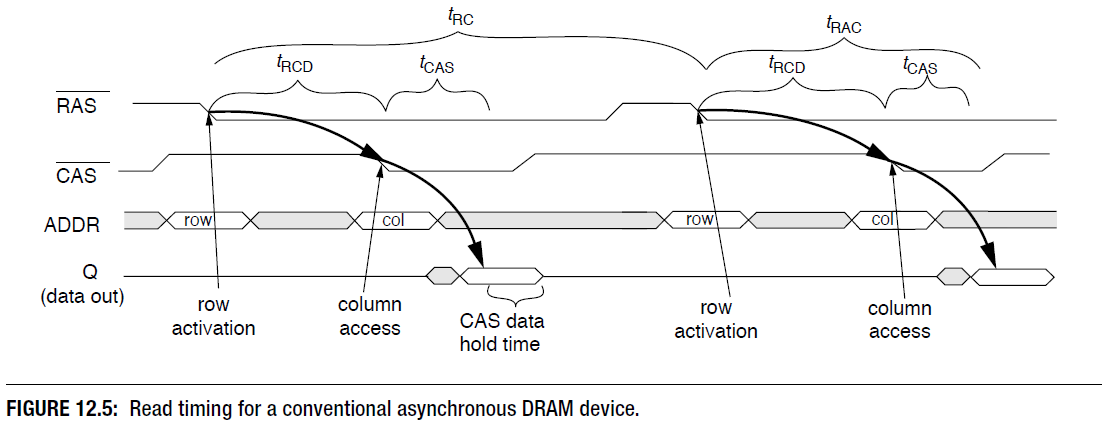

이러한 비동기 디바이스는 이전의 클럭 기반 디바이스들과 같이 모든 액세스는 로우 활성화와 이후 칼럼 액세스 단계를 거쳐야만 했다. 즉, 마이크로프로세서가 이전의 데이터와 같은 로우에 있는 데이터를 요구하여도, 전체 로우 활성화와 칼럼 액세스 프로세스가 다시 반복되어야 했다. 그림 12.5는 비동기 디바이스의 타이밍을 나타낸다. 어떤 2개의 어드레스로부터 데이터를 옮기기 위해서는 2번의 전체 로우 사이클이 필요함을 나타낸다.

12.2.3 FPM DRAM

1103 디바이스가 소개된후 새로운 기능을 도입했다. Page Mode operation 이다. 모든 Row(Page)의 데이터는 DRAM 디바이스 내부의 Sense amplifier들에 의해 유지되고, 같은 로우에 있는 데이터는 칼럼 액세스만으로 다른 latency 없이 접근할 수 있다. 해당 오퍼레이션은 성능을 개선시키고, 특정 어플리케이션에게 Spatial Locality 의 메모리 액세스 패턴의 이득을 제공한다.

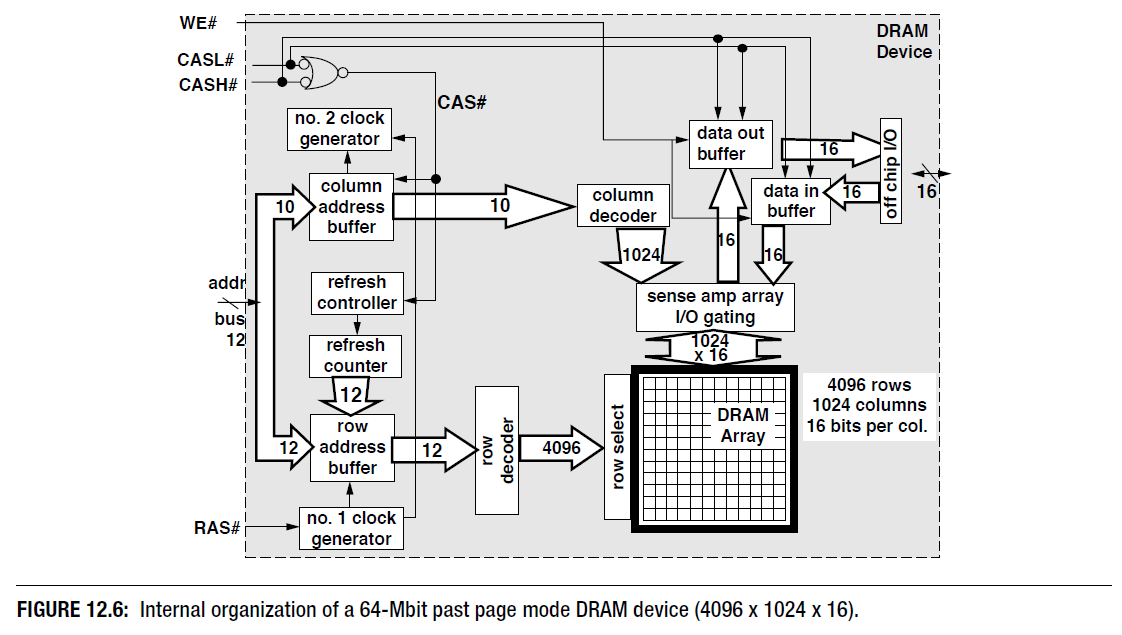

해당 오퍼레이션은 Sense amplifer가 외부에 있던 초기 디바이스에들에선 불가능하다. 이후 내부에 집적되면서 가능하게 되었고 전체 로우가 병렬로 연결된 Sense amplifer에 의해 한꺼번에 Sensing, Buffer 될수 있었다. 따라서 FPM은 1980년대 초기의 많은 64-kbit DRAM디바이스에서 사용되었다. 해당 메모리는 1990년대까지 상용 메모리의 주류였으며, EDO DRAM에 의해 대체되었고 최종적으로 SDRAM에 의해 완전히 대체되었다. 그림 12.6은 16bit wide 양방향 데이터 버스를 가진 64-Mbit FPM DRAM을 나타나낸다.

그림 디바이스 내부의 DRAM 스토리지 셀들은 4096개의 로우들과 각 로우마다 1024개의 칼럼을 가지며 칼럼마다 16bit의 데이터를 가진다. 로우 어드레스는 어드레스 버스에 놓이고, 외부 컨트롤러에 의해 RAS/가 전달된다.

해당 디바이스에서 로우 액세스가 일어날때마다 DRAM 디바이스 내부에서 어드레스 버스는 로우 어드레스 버퍼에 의해 버퍼된 이후에 로우 디코더로 보내진다. 이후 로우 어드레스 디코더는 로우 어드레스를 받아들여 스토리지 셀들이 있는 4096개의 로우중에 1개를 선택한다. 선택된 로우의 스토리지 셀들에 저장된 값들은 Sense amplifer들에 의해 센싱되고 활성화된다. 16bit의 크기의 칼럼은 이 디바이스의 접속가능한 기본 메모리 단위이며, 칼럼 액세스 명령에 의해 16bit의 데이터를 읽거나 쓰는 동작을 수행한다. CASH 는 16bit의 절반인 8bit에 독립적으로 접속이 가능하다.

칼럼 액세스 커맨드는 로우 커맨드와 비슷하다. 칼럼 어드레스를 어드레스 버스에 놓고 적절한 CAS/신호를 인가한다. 내부적으로 DRAM칩은 칼럼 어드레스를 받아들여, 디코드하고 1024개 칼럼들중 하나를 선택한다. 칼럼 read 커맨드의 경우 해당 칼럼의 데이터는 DRAM 디바이스의 데이터 버스에 놓이고, WE(Write enable) 신호에 따라 메모리 컨트롤러로부터 데이터로 덮어 써지기도 한다.

그림 12.7은 FPM디바이스의 페이지 모드 Read에 대해 보여준다. RAS/신호가 low되어 로우가 활성화 되면, 같은 DRAM 로우의 인접한 데이터를 다수의 칼럼 액세스를 사용하여 페이지 모드 사이클 타임인 tPC이후 접속이 가능함을 보여준다. 또한 출력 데이터 유효시간이 CAS/신호의 타이밍에 따라 제어되는 것을 보여준다. 즉, CAS/신호가 높게 된 일정시간 이후에도 DRAM디바이스의 Read 데이터 출력이 유지된다.

프리차지 커맨드나 로우 액세스 커맨드 없이 다음 칼럼 액세스 커맨드를 준비한다. FPM DRAM 디바이스에서 페이지 모드 사이클 타임은 로우 사이클 시간의 1/3 정도로 짧아질 수 있다. 결론적으로 페이지 모드 오퍼레이션은 DRAM디바이스의 Spatial상으로 인접한 데이터에 대한 대역폭을 페이지 모드 오퍼레이션이 없는 비동기 DRAM 디바이스에 비해 3배정도 증가시켰다.

'책 > 메모리 시스템' 카테고리의 다른 글

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-3' (0) | 2021.10.28 |

|---|---|

| 메모리 시스템 Ch12_'DRAM 장치 구조의 혁신적인 발전-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-4' (0) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-3' (0) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-2' (0) | 2021.10.28 |