Abstract

NVM 기술이 Main Memory의 대체 가능한 기술로 부상함에 따라, 아키텍쳐 레벨에서의 performance, energy, reliability의 분석이 필요해졌다.

NVmain이라고 칭하는 시뮬레이터는 DRAM, NVM 모두를 지원하며 설계를 할 수 있도록 지원한다.

1. Intro

최신 ITRS로드맵에서 현재 DRAM이 직면하고 있는 일부 문제에 대한 솔루션은 아직 존재하지 않는다.

또한 DRAM은 전력 소모량에서 많은 단점을 가지고 있다.(3D Stacked DRAM 개발이유)

DRAM의 Refresh, stand-by power는 큰 전력 소모의 두가지 주요 요인이다.

NVM의 본질적인 특성은 데이터가 손실(lost)되지 않는다는 점이다. 이는 데이터가 Refresh할 필요가 없다는 뜻과 동일하다.

하지만 NVM의 Write 시의 사용 전력이 높기 때문에 Refresh하지 않는 절감 효과를 상당 부분 앗아 갈 수 있다.

DRAM에서 NVM으로의 변화는 간단한 문제가 아니다. 그중에서는 NVM의 Long Latency Time 이 문제가 된다.

특히 Write Latency가 DRAM에 비해 몇배가 될 수 있다. 그러나 이는 Memory Cell의 특성이므로 최적화하기 어렵다.

또한 NVM은 DRAM에 비해 Memory Cell의 내구도가 낮다.

보통 DRAM의 내구성은 10^15, PCM의 내구성은 10^8 - 10^9 사이다. 낮은 내구성 때문에 Hard fault를 모델링 하는 것 또한 중요하다.

해당 논문에서는 하이브리드 설계를 포함한 DRAM 및 NVM 모두에서 Energy, Cycles이 정확한 Architecture Level을 소개한다.

Memory Cell의 작동 보다, Column, row, bank, rank, caannels로 구성된 계층에 대해 접근한다.

2. Simulator Overview

Single Bank Memory의 작동은 매우 단순한 State Machine이다. Bank의 크기가 크면 높은 Latency를 초래한다.

Main Memory는 일반적으로 공통적인 Bus를 사용하는 Multiple Bank로 구성된다.

아래의 그림은 가장 일반적인 DDR 기반 전송 Bus를 나타낸다.

(Single Rank, N devices, 각 Device들은 여러개의 Bank와 Single row buffer를 가진다, 각 디바이스는 4, 8 or 16bits를 출력한다)

이러한 상태에서의 복잡성은 여러 Bank가 그룹화되고 동일한 버스를 공유할때 발생한다.

메모리 컨트롤러는 여러 Bank에 issue된 명령이 Bus를 동시에 제어하지 않도록 해야한다.

따라서 뱅크에서 발생할 수 있는 대기 시간이 있으므로 단일 메모리 요청 시간은 정적이지 않다.

많은 Rank를 가지면 shared interconnect 사이의 Contention이 증가 할 수있다. 이는 Queuing Latency에서 찾아 볼 수있다.

약간의 차이가 있는 메모리 대기 시간의 평균값을 사용하는 정적 메모리 모델은 Contention이 심한 메모리를 모델링하는데 적합하지 않다.

Queuing Latency는 Queue의 항목수에 따라 기하 급수적으로 증가하므로 부정확해 진다.

오늘날 Main Memory는 단일 Device의 전력을 제한하고 여러 Bank가 동시에 작동할때 최대 전류 소모량을 제한한다.

이러한 제약은 추가적인 Latency를 발생한다.

NVM에서 추가 타이밍 제약 조건경우를 고려하여 여러 뱅크의 Activation이 겹치는 동안 최대 전류 요구량을 제한하기 위해 Row to Row Activation(tRRD)가 도입된다.

NVM의 경우 Write Energy가 Read Energy에 비해 매우 높다. 따라서 여러 Bank 에서 Activation과 Write Energy가 겹치는 경우 매우 큰 전력 Spike가 발생 할 수 있다.

기존의 Simulator들은 hard-fault에 대해 처리를 하지 않는다.

DRAM의 정보들은 Datasheet에서 가져오며, NVM에 대한 정보들은 정해진 표준이 존재하지 않아 CACTI, NVMSIM에서 정보를 가져온다.

A. NVM Timing Model

Single Bank Timings

DRAM 시스템은 Read/Write cycle이 거의 동일하게 작동함으로 가정한다.

Read는 Memory Cell의 파괴를 초래함으로 Row Close 시에 해당 row를 DRAM Array로 Restore 하고 Pre-charge를 실행해야 한다.(NVM은 불필요)

Restore Time은 DRAM의 동일한 Bank내의 연속 Read를 금지할 수 있다. 일반적으로 Restore Time은 Column Read 보다 훨씬 느리다.

--In DRAM--

tRC = Entire Read Cycle = tRCD + tRAS + tRP (가장 빠른 시간)

tRAS = Restoration Time

tRCD = Activation Time

tRP = Precharge Time

tRC는 tRRD(Row to Row), tFAW(four window) Latency를 제외할 경우 Main Memory Bank에서 다른 Row를 Read할 수 있는 사이 시간이다.

--In NVM--

DRAM과 다르게 Restore가 필요 없으므로 tRAS = 0를 사용한다.

tRC = tRCD + tBURST + tRP (가장 빠른 시간)

DRAM에서 tRAS는 tRCD + tCL 시간보다 훨씬 길다.

tRAS는 tBURST보다 5~7배 이다.

따라서 NVM에서 다른 행에 대한 무작위 읽기는 DRAM 에서의 Row Activation, Precharge에서 DRAM보다 빠를 것이다.

Inter Bank Timings

이산 시간내에 전력 및 전류 소모량을 줄이기 위해 tFAW(for Four Acitivation Window)와 tRRD(Row to Row Activation Delay)가 도입되었다.

tFAS = 4개의 Activation이 발생할 수 있는 최소 시간 간격

tRRD = 동일 디바이스의 Row Activation 사이의 최소 시간

NVM에서는 Write Energy가 매우 높으며 Latency 또한 매우 길어서 다른 Row Activation 및 Write와 겹쳐 소모에너지 폭발이 나타날 수있다.

따라서 tWWD(Write to Write Delay) tWAD(Write to Activation Delay) tAWD(Activation to Write Delay)를 추가한다.

Determining NVM Timings

NVM을 위한 Timing을 얻기위해 NVSIM을 사용한다. RRAM, PCM, STT-RAM 등이 지원된다

단일 뱅크를 위한 Area, Latency, Energy, Energy Delay product의 제약조건을 설계할 수있다.

Activation or Precharge를 포함하여 Read에 필요한 Cycle Parameter들을 제공한다.

Activation or SET, RESET of NVM cell or Precharge를 포함하여 Write에 필요한 Cycle Parameter를 제공.

Main Memory는 일반적으로 여러개의 Devices로 구성되기 때문에, NVSIM에서 시뮬된 Physical Bank는 read/write에 Access되는 Logical Bank의 용량보다 작다.(8bit 워드, 16MB Physical Bank 설계 시 64bit, 128MB Logical Bank)

즉 1개의 Devices 내 1개의 Bank가 Physical Bank, 해당 Bank과 동일하게 활동하는 Bank가 Logical Bank

(보통 1Rank, 8Devices, 8bit/Device 이므로 Physical * 8 = Logical 이다)

각 Device에는 여러개의 뱅크가있으며 이를 Physical Bank라고 정의, 8개의 Device가 동시에 Access하기 때문에 전체 뱅크는 실제로 8배 크다(8 Device) 이를 Logical Bank라고 한다.

Bank에서 Write를 처리하기 위해 BUS로부터 제공된 Data는 Sense Amp로 기록된다고 가정한다. 해당 Bank가 Precharge 하면 Amp의 Data가 Memory cell에 기록된다. 이를위해 (tWR)Write Latency를 사용하여 모델링한다. 즉 Write와 Precharge 사이의 시간만 지정하므로 무작위 Read가 매우 빠르게 발생 할 수 있다.

B. NVM Power Model

Energy Mapping의 경우 NVSIM에 의해서 Read/Write 정확한 값을 모두 사용한다.

Row Activation Command에 대해 Activation Energy값은 각 Devices의 각 Bank 또는 Physical Bank의 총 에너지 소비량에 추가된다.

각 Physical Bank는 64bit를 Read할 때 Lock-step으로 Open되기 때문에 모든 N devices 장치로 부터 총 시스템 에너지 값이 추가된다.

즉 Activation Energy는 Open된 모든 Bank의 Activation Energy를 합한 값이다.

Row는 오랫동안 Open상태를 유지할 수 있기 때문에, Read/Write 명령중에만 R/W Energy를 추가한다.

또한 SET bit(‘1’) RESET bit(‘0’)에 필요한 Energy도 추가하였다.

3. Verification

Timing과 Power에 대해 Verification을 수행했다.

A. Timing Verification

Bank Level의 타이밍 확인은 소스코드에 자동으로 제공된다. 잘못된 작업을 시도하면 Error Message가 출력된다.

예를들어 Activating Open Row, Reading a Closed Row, reading to a non-open row, precharging a closed row 등이 있다.

Rank Level에서 Bus Diagram은 메모리로 보내거나 메모리에서 보내는 특정 명령을 보여주는 옵션을 활성화 할 수 있다.

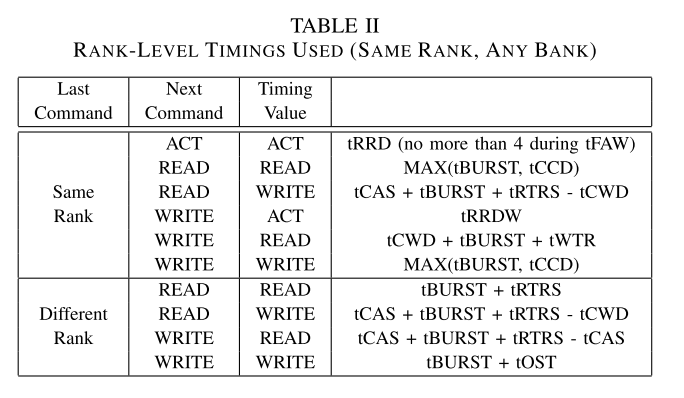

Table 1은 Bank Level에 사용되는 Timing을 나타낸다. 이전 명령이 주어진 단일 Bank 시스템에서 다음 명령이 실행되는 시간이다, 따라서 이전 명령과 다른 Bank에 실행되는 명령을 issue하기 위해서는 Table 2의 Timing도 고려해야한다.

B. Power Verification

DRAM Data sheet와 DRAMsim을 이용해 쉽게 비교할 수 있기 때문에 전류 기반 DRAM 전력 모델의 검증도 수행했다.

DRAM 전력 모델을 두가지 측면에서 정확성을 확인했다. 먼저 DRAM caculator에 Value를 연결하여 Total power, Background current, activation, burst, and refresh current를 계산했다.

C. Endurance Model Verification

내구성 모델링의 아이디어의 간단한 설명은 메모리에 대한 쓰기 작업이 발생할 때, 변경된 Bit만 Write 하는 것이다. 기존 DRAM System에서는 Capacitor의 전하를 감지하고 파괴하여 전체 Row를 읽는다. 그런다음 Read가 발생한 후 이 데이터를 다시 Capacitor로 복원 해야한다. Write의 경우 Read와 유사한 방식으로 읽고 업데이트한 후 Capacitor Cell로 다시 복원한다. 이를 NVM에 동일하게 적용하면 일부 Bit가 불필요하게 업데이트 된다.

현재 메모리는 캐시라인에 의해 Write되고 Read된다. 이 경우 값을 2에서 3으로 업데이트 하는 NVM은 512Bit중 단 1Bit만 변경된다. 이 경우 나머지 Bit의 수명을 위해 업데이트 할 Bit만 Write 해야한다. 이는 Memory Cell에 Write 하기전 Bit를 비교해야함으로 Data Comparison Write(DCW) 라고 하며 다른 논문에 설명되어있다.

FlipNWrite의 기술과도 비교했으며, 이는 메모리의 특정 파티션(eg. 32Bit, 64Bit)에 대해 Write될 Bit 수를 세는 것이다. 업데이트 해야할 bit 수가 이 파티션의 절반 이상이면 데이터가 반전되고 Flip된 Bit가 설정된다.

결과적으로 FlipNWrite가 DCW보다 더 잘 수행되었다.

4. Case Studies

서로 다른 Memory Controller를 비교하는 방법을 시연한다. NVM의 가장 중요한 문제는 Write와 관련이 있기 때문에 Mem Controller Scheduling은 성능과 전력면에서 차이를 만든다. 두 개의 간단한 컨트롤러와 Fig 1에 표시된 모델과는 다른 상호 연결에서 실행되는 최근에 제안된 Memory Controller와 비교한다.

PCM의 경우 Write Latency가 길기 때문에 Mem Controller는 Write 및 Read를 다른 Queue로 분할 하려고 시도할 수 있으며, Write의 우선 순위가 매우 낮다.

여기서 비교한 간단한 컨트롤러는 Close Page Mode FCFS와 First Ready FCFS이다. FCFS는 말그대로 컨트롤러에 도착하는 순서대로 전송한다. FR-FCFS는 Row buffer hit 이나 target bank 가 close 되고 Data가 포함된 Row를 Activate할 수 있는 요청에서 Issue Queue를 Search한다.

보다 고급화된 컨트롤러는 Stack Controller이다. 이는 Memory Bank가 언제 Ready될지를 추측하여 작동한다. Row activate, burst read, precharge timing과 Memory latency value(ML)이 추측 값으로 사용된다.

5. Conclusion

NVM와 DRAM 모두 모델링 하도록 설계했다. Single Bank의 Basic Model에서 Channel Level에 대한 확장에 대해 논의했다. NVM의 하위 레벨 회로 시뮬레이터 입력을 사용해 전력을 추정하는 방법을 탐구 했다.