SRAM = Static RAM

전원이 공급되면 데이터는 유지

DRAM = Dynamic RAM

만약 아무것도 하지않는다면 데이터 손실

SRAM: 6T per bit

일반적인 고속 CMOS 기술로 구현

DRAM: 1T per bit (+1 capacitor)

Density에 최적화된 DRAM process

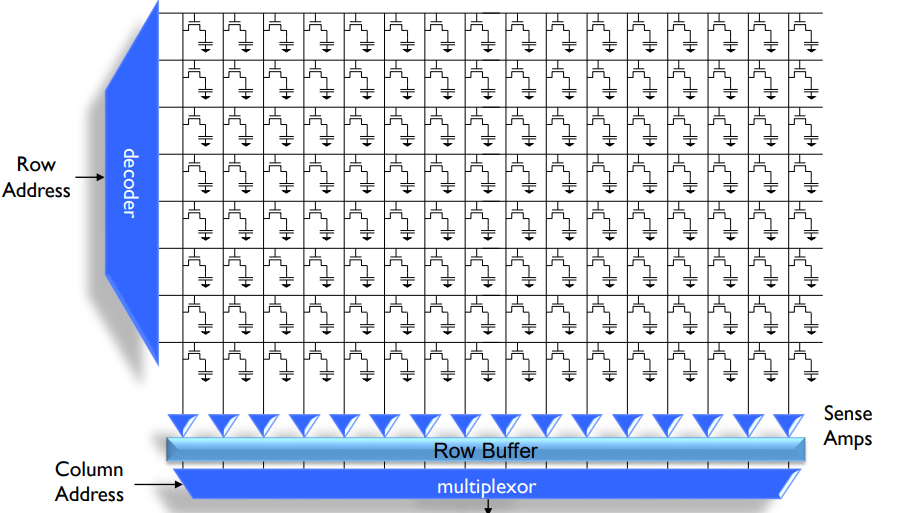

DRAM의 Low-Level Organization은 SRAM과 유사하다.

Read의 경우 매우 파괴(Destructive)적이며, Read에 의해 내용이 지워진다.

Row buffer는 Read Data를 유지한다.

- Row buffer의 Data를 DRAM Row라고 한다

- 종종 Page 라고 불리운다. (Virtual Memory의 Page와 혼동)

- Block Read는 항상 Row buffer에서 수행된다.

- 전체 Row을 Read 하지만 하나의 Block에 Access

- Cache line을 읽는것과 비슷하지만 하나의 word에 Access

Read후 DRAM cell의 Data는 삭제

- Row buffer의 Data는 그대로 저장되어 있다.

다른 Read를 수행하기전에 bit Write 실행

cell에서 buffer로의 read는 느리지만 buffer에서의 read는 빠르다.

- buffer로 부터 mutiple lines를 읽는다,(Row buffer hit)

아무것도 하지않아도 Cell의 Data는 점차 삭제됨(이것이 Dynamic RAM 이유)

따라서 DRAM은 정기적으로 Read and Re-write를 시행해야한다.

Burst Refesh

모든것을 멈추고 All Memory에 대해 Refresh

Distributed Refresh

한번에 하나(또는 몇개)의 Row를 Refresh

장시간 메모리 차단 방지

Self-refresh (Low-Power mode)

DRAM에게 자체적인 Refresh를 지시

Memory Controller의 종료

Self-Refresh를 종료하는데 시간이 소요

'개인 공부 > 메모리' 카테고리의 다른 글

| MSHRs(Miss Status Holding Register) (1) | 2021.06.10 |

|---|---|

| DRAM Operation, Memory Control & Memory Latency - 3 (2) | 2021.06.08 |

| DRAM Operation, Memory Control & Memory Latency - 2 (0) | 2021.06.07 |

| DRAM Operation, Memory Control & Memory Latency - 1 (2) | 2021.06.07 |

| 메모리 타이밍 (0) | 2021.03.09 |