11.1.3 로우 액세스 커맨드

그림 11.3은 로우 액세스 커맨드의 대략적인 진행을 보여준다. 이는 Row Activation 커맨드라고도 불린다. DRAM 어레이들의 셀에있는 데이터를 Sense Amplifier로 이동시키고, 다시 DRAM 어레이의 셀로 복원시키는데 사용된다.

관련된 타이밍으로 tRCD, tRAS가 존재한다. tRCD(Row-Column(Command) Delay)는 로우 액세스 커맨드로부터 DRAM 셀 어레이들의 데이터를 Sense Amplifer로 옮기는데 걸리는 시간을 의미한다.

tRCD 이후 데이터는 사용할수 있지만, 복원(Restore)은 완전히 하지않은 상태다. tRAS(Row Access Strobe lantency)는 로우 액세스 커맨드의 입력으로 부터 DRAM 셀의 로우 데이터 방출과 복원에 걸리는 시간이다. tRAS 이후에 복원을 수행하고, Sense Amplifer가 동일한 DRAM 어레이의 뱅크에 있는 다른 로우 액세스를 위해 Precharge가 수행된다.

11.1.4 칼럼 Read 커맨드

그림 11.4는 칼럼 Read 커맨드의 진행을 보여준다. DRAM 어레이들의 정해진 뱅크의 Sense Amplifer 어레이로부터 데이터 버스를 통해 메모리 컨트롤러로 데이터를 전송한다. 관련된 타이밍으로 tCAS, tCCD, tBURST로 세가지가 존재한다.

tCAS(Column Access Strobe latency)는 칼럼 Read 커맨드 입력 이후에 DRAM 디바이스로부터 요청한 데이터를 데이터 버스에 배치하기 까지 걸리는 시간이다. 오늘날 디바이스는 내부적으로 짧게 데이터를 전송하고 연속적으로 버스트를 한다. 그림 11.4는 내부적으로 두번의 짧은 버스트롤 통해 데이터를 전송하는 상황이다.

tCCD(Column to Column Delay)는 최소 버스트 기간 혹은 최소 Column-to Column 커맨드 타이밍을 의미한다. 해당 최소 버스트 기간은 DRAM디바이스의 프리페치 길이에 의해 결정된다. (ex, DDR에서 Prefetch 길이 = 데이터의 2 beat라면 tCCD는 하나의 Full Cycle)

tBURST는 하나의 칼럼 Read 커맨드일 때 데이터 버스의 버스트 기간이다.

tCCD가 tBURST보다 작은 경우, 데이터 버스를 통해 데이터 전송하는 속도는 tBURST에 의해 결정된다. 따라서 칼럼 액세스 커맨드의 프리페치 길이는 프로토콜에 영향을 주지않는다. 하지만 큰 경우, 인트라 랭크 칼럼(Intra-rank column) 칼럼 액세스 커맨드들이 tCCD에 의해 제한된다. 이런 경우 외에도 칼럼 Read 커맨드가 Precharge 커맨드 직후에 발생하는 경우에 프리페치 길이의 차이가 프로토콜에 영향을 준다.

11.1.5 칼럼 Write 커맨드

그림 11.5는 칼럼 Write 커맨드의 진행을 나타낸 그림이다. 메모리 컨트롤러로 부터 목표 뱅크의 Sense Amplifer로 데이터를 전송한다. Read와 유사하디만 데이터 전송 방향에 차이가 있다.(read 커맨드의 처리단계를 반대로 진행한다)

tCWD(Column Write Delay)는 칼럼 Write 커맨드가 커맨드 버스로 입력된 시점으로부터 메모리 컨트롤러에 의해 write 데이터가 데이터 버스에 위치하는 데까지 걸리는 시간이다. 각 프로토콜들은 서로다른 tCWD를 가진다. 그림11.5에서 SDRAM은 칼럼 Write 커맨드와 동시에 write 데이터가 데이터 버스에 위치하는 것을 확인 할 수 있다. DDR 경우 tCWD는 1 클럭 사이클이며 DDR2는 tCWD가 tCAS 보다 1사이클 작은 값을 가진다. DDR3경우 5~8 사이클의 값을 선택적으로 가진다.

tWR(Write Recovery)는 Write 데이터가 DRAM 어레이들로 전파되는데 걸리는 시간으로 Write 커맨드 직후 Precharge 커맨드를 전송하기 위해 대기해야하는 최소 시간이다.

tWTR(Write to read Tunaround 시간)은 I/O 게이팅 자원들이 Write 커맨드에 의해 방출되는 데 걸리는 시간으로 Write 커맨드 직후 Read 커맨드를 전송하기 위해 대기해야하는 최소 시간이다.

11.1.6 프리차지 커맨드

DRAM 디바이스의 데이터 액세스는 두개의 과정을 거친다. 먼저 로우 액세스 커맨드가 데이터를 셀 어레이로 부터 Sense Amplifier 어레이로 이동시킨다. 로우 액세스 커맨드에 의해 데이터가 모두 이동하고나면, 데이터는 Sense Amplifer에 의해 증폭되고 후의 칼럼 액세스 커맨드에 의해 디바이스로부터 DRAM 컨트롤러로 이동하게된다. 로우 액세스 시퀸스의마지막으로 프라치지 커맨드가 Sense Amplifer의 Bit Line을 리셋하여 새로운 로우 액세스 커맨드가 동일한 셀 어레이에 오는 것을 대비한다.

그림 11.6은 프리차지 커낸드의 진행을 나타낸다.

tRP는 프리차지 커맨드 입력 이후에 선탱된 뱅크의 Bit Line과 Sense Amplifer가 프리차지 되는데 걸리는 시간을 말한다.

tRP, tRAS를 조합하여 tRC(Row Cycle)을 얻을 수 있다. tRC란 DRAM 디바이스가 DRAM 셀 어레이로부터 Sense Amplifer로 이동시키고, DRAM 셀에 데이터를 복원하고, 프리차지하여 다음 로우 액세스 커맨드를 준비하는데 걸리는 최소 시간이다.

11.1.7 리프레시 커맨드

DRAM은 비영구적인 저장 캐피시터로 인해 주기적으로 데이터를 복구해주어야 한다. 다만 리프레시 동작은 대역폭과 파워를 소모하는 것이 해당 메커니즘의 단점이다. 시스템마다 다른 리프레시 메커니즘을 사용한다.

대부분의 DRAM 디바이스는 리프레시 로우 어드레스 레지스터를 사용하여 마지막으로 리프레시한 로우의 어드레스를 기억한다. 일반적으로 메모리 컨트롤러는 하나의 리프레시 커맨드를 전송하고, 디바이스는 리프레시 로우 어드레스 레지스터의 값을 하나씩 증가시키는 것을 통해 모든 뱅크의 로우를 리프레시 한다.

즉 기본적인 전체 뱅크에 대한 병행 처리 리프레시 커맨드가 나오면, DRAM 디바이스는 리프레시 어드레스 레지스터로부터 로우 어드레스를 가져오고, 모든 뱅크의 해당 로우 어드레스가 동시에 리프레시 되도록한다.

tRFC(1 Refresh Cycle Time)은 모든 뱅크로 하나의 리프레시 커맨드를 전송하면 완료까지 소모되는 시간이다.

표 11.2 는 DDR, DDR2 의 리프레시 타이밍을 나타낸다. 밀도가 증가함에 따라, 리프레시해야하는 셀의수도 증가했다. 여기서 한 해결법은 큰 용량의 DDR2 디바이스에 대하여, 로우 개수가 두배로 증가해도 리프레시 커맨드 주기를 64ms로 유지하는 방법이었따다. 결과적으로 디바이스 용량과 무관하게, 메모리 컨트롤러가 8192번의 리프레시 커맨드를 매 64ms마다 DRAM 디바이스로 전송해야한다. 그러나 대용량의 경우 8192개 넘는 로우가 존재하고 이때문에 리프레시 커맨드는 2,4,8 개의 로우를 한번에 리프레시 해야한다.

11.1.8 Read 사이클

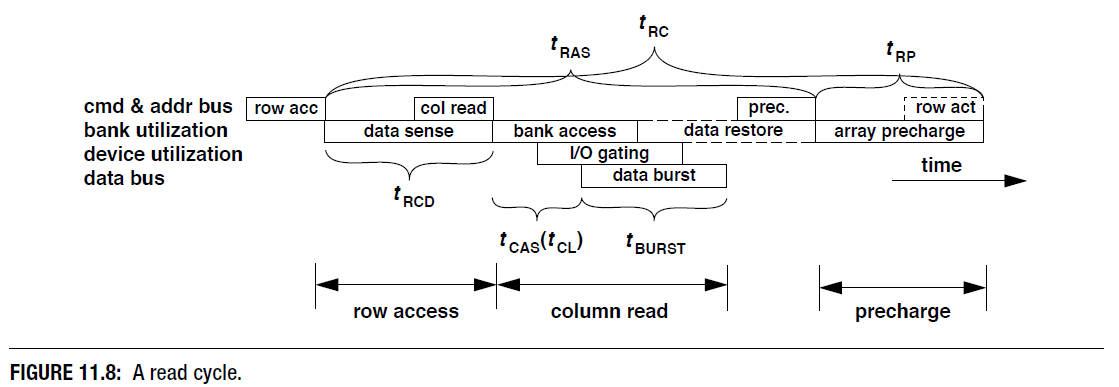

그림 11.8은 SDRAM, DDRx SDRAM과 같은 일반적 메모리 시스템의 Read 사이클을 보여준다. 현대의 디바이스경우 각각의 로우 액세스 커맨드가 정해진 뱅크의 Sense Amplifer 어레이로 수천비트의 데이터를 전달한다. 이후 칼럼 Read 커맨드는 이중에 수십에서 수백비트의 데이터를 버스를 통해 메모리 컨트롤러로 전달한다. Row Locality가 높은 경우에는 활성화된 데이터를 유지하는것이 유리하고(Open Page), 낮은 경우에는 액세스 직후 바로 Precharge 하여 다른 로우에 액세스 하도록 대비하는것이 유리하다.(Close Page)

그림 11.8은 DRAM 셀의 하나의 뱅크로 빠르게 액세스하는 일련의 커맨드를 보여준다. 셀로부터 Sense Amplifer로 데이터가 이동하고, tRCD이후에는 요청한 로우의 데이터가 Sense Amplifer에 의해 결정되고, 메모리 컨트롤러가 디바이스로 칼럼 Read, Write커맨드를 전송할 수 있게 된다. 컬럼 액세스 커맨드 전송 직후에, 디바이스는 곧바로 Sense Amplifer의 데이터를 DRAM셀에 복구한다. 이후 최초의 로우 액세스 커맨드 입력이후 tRAS시간이 지나면, Bit Line과 Sense Amplifer를 초기화하는 프리차지 커맨드를 수행하기 위한 준비를 마친다.

11.1.9 Write 사이클

그림 11.9는 일반적인 메모리 시스템의 Write 사이클을 보여준다. 오늘날의 로우 사이클 시간은 Write 사이클의 지속시간에 의해 제한된다. 즉 로우 사이클 시간은 디바이스가 임의의 데이터를 셀의 정해진 뱅크의 임의의 로우로 전송하기 위한 최소한의 시간을 의미한다.

Write 액세스 경우 데이터는 메모리컨트롤러로 부터 공급, 데이터 버스를 통해 드라이브되어 I/O 게이팅 멀티플렉서를 통과한후, Sense Amplifer를 오버드라이브하여, 셀에 저장된다. 이 과정은 프리차지 커맨드가 진행되기전 모두 완료되어야 한다. 즉 tRAS는 tRCD, tCWD, tCCD, tWR를 처리할 수 있을만큼 충분히 길어야한다.

11.1.10 복잡한 커맨드들

일부 DRAM 디바이스는 복잡한 일련의 동작을 수행하는 복합 커맨드를 지원하기 위해 설계되었다. 그림 11.10은 그림 11.8과 동일한 시퀸스를 보여준다. 그러나 11.8의 칼럼 Read 커맨드는 11.10에서 Column-read-and-precharge 커맨드로 대체되었다. 이것의 장점은 칼럼 액세스 직후 프리차지하는 Close Page 시스템을 위해 2가지 커맨드를 1개로 축소했다.

DDR2 SDRAM과 같은 오늘날 DRAM디바이스에는 Column-read-and-prechage 커맨드의 Auto-prechage 성분이 tRAS 타이밍 조건을 위반하지 않도록 tRAS lockout이름의 기능이 구현되어있다.

두번째로 지원하는 복잡한 커맨드는 posted 칼럼 액세스(posted CAS/) 커맨드이다. 이는 단순히 동작의 수행이 디바이스에서 고정된 몇 사이클 지연된 칼럼 액세스 커맨드이다. 그림 11.11은 tAL로 설정된 값에 기반하여 CAS/ 커맨드 동작을 지연시킨다.

Column-read-and-precharge는 흔히 column-read-command with auto-prechage라고도 한다. 그림 10.10과 그림 10.11의 차이는 column-read-and-prehcage 커맨드가 posted CAS/커맨드이며, 그림 11.11에서는 posted column read 커맨드가 로우 액세스 이후 직후에 발행되었다는 점이다. 하지만 tRCD의 조건을 위반하지 않도록하기위해 tAL의 값에의해 연기되었다.

'책 > 메모리 시스템' 카테고리의 다른 글

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-4' (0) | 2021.10.28 |

|---|---|

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-3' (0) | 2021.10.28 |

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-1' (0) | 2021.10.28 |

| 메모리 시스템 Ch10_'DRAM 메모리 시스템 구조-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch10_'DRAM 메모리 시스템 구조-1' (0) | 2021.10.28 |