Chapter 10 DRAM 메모리 시스템 구조

DRAM 메모리 시스템에 있어서 기본적인 용어들과 블럭 구조에 대해서 설명한다.

자수의 DRAM 디바이스들의 구현, 구성, 동작을 설명하고 다양한 종류의 메모리 모듈의 구조와 함께 용어 및 토폴로지에 대한 내용을 담겠다.

10.1 종래의 메모리 시스템

DRAM 디바이스의 저장 크기는 제조공정, 셀, 배열 효율, 수율 향상을 위해 결함 셀을 재배지하는 메커니즘의 효율성 등에 의해 제한된다.

즉, 단일 DRAM 디바이스에 있는 저장 크기는 전문 임베디드 시스템을 제외하고 대부분의 컴퓨팅 플래폼을 위한 메인 메모리로서 불충분한 상태를 지속적으로 유지하고 있다.

이 장에서는 비용과 성능을 개선하기 위한 다른 멀티칩 DRAM 메모리 시스템 구조와 연결 방식에 대하여 설명하도록 한다.

위 기름은 단일 메모리 컨트롤러에 의해 제어되는 하나의 메모리 시스템을 형성하도록 다수의 DRAM 디바이스가 연결된 것을 보여준다.

오늘날 컴퓨터는 하나 이상의 메모리 컨트롤러가 포함되어있다.(프로세서 패키지 및 외부 시스템 컨트롤러로 존재)

메모리 컨트롤러는 아래와같은 순서로 기능을 수행한다.

1. 메모리에 주어진 어드레스에 Read/Write 요청을 처리

2. 해당 요청을 메모리 시스템의 커맨드로 변환

3. 적절한 타이밍에 적절한 순서대로 DRAM 디바이스에 해당 명령을 실행

4. 프로세스나 시스템의 I/O 디바이스를 대신해 데이터를 검색/저장

10.2 기초적인 명명법

다수의 DRAM 디바이스 구조는 저장 용량, 동작 속도, 접근 시간, 대역폭 특성의 측면에서 메모리 성능에 영향을 준다.

따라서 잘 정리된 명명법의 일반적인 기초 없이는 DRAM 메모리 시스템에 대한 논의에 있어서 기술 문서 및 데이터 시트가 때대로 혼란만을 가중시킬수 있다. 해당 절에서는 채널, 랭크, 뱅크, 로우, 칼러의 용어에 대해서 정의하도록 하겠다.

10.2.1 채널

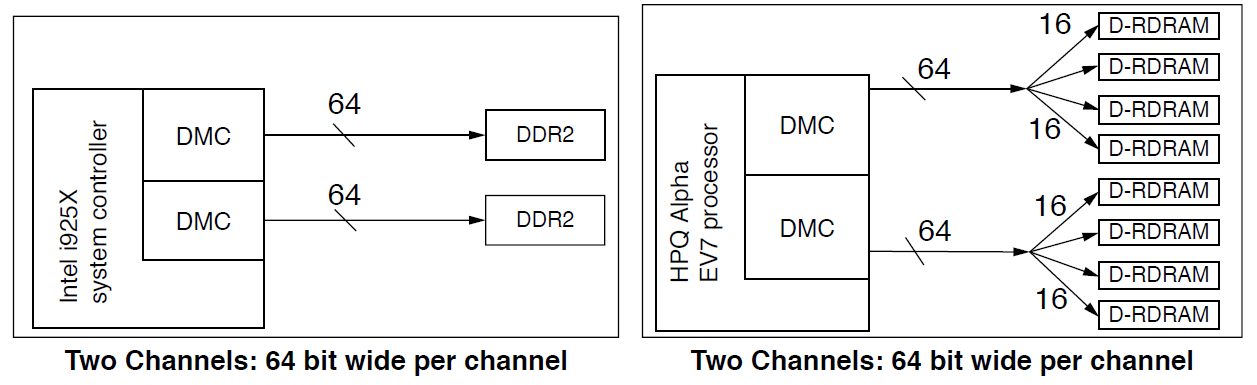

위 그림은 메모리 시스템의 구성이 미묘하게 다른 세 가지 시스템 컨터롤러를 보여주고 있다. 각 시스템 컨트롤러는 하나의 DRAM Memory Controller(DMC)를 가지고 있고, 각 DRAM 메모리 컨트롤러는 하나의 채널을 제어한다.

"typical" 명명된 부분에서 시스템 컨트롤러는 하나의 64bit 와이드 채널을 제어한다. 오늘날의 범용 DRAM 메모리 모듈에는 64bit 와이드의 데이터 버스로 표준화 되었다.

"i875P" 명명된 부분에서 시스템 컨트롤러는 128bit 와이드 데이터 버스를 가지는 DRAM의 단일 채널에 연결된다. 하지만 범용 메모리는 64bit 로 동작하기 때문에 64bit 와이드 메모리 모듈 쌍을 요구한다. 이러한 구성을 "듀얼 채널"구성이라고도 불린다.

"i850" 명명된 부분에서 standard Direct RDRAM로 구성되고 이 메모리 모듈들은 16bit 와이드 데이터 버스로 설계되었다. 더욱이 Direct RDRAM을 사용하는 고성능 시스템 컨트롤러들은 메모리의 두 물리적 채널을 오가며 동작하는 32bit 채널 폭을 구성하기위해 동일한 쌍의 Direct RDRAM 메모리 모듈을 사용한다.

위 그림은 64bit 폭의 데이터 버스들을 독립적으로 동작시키기 위해 두개의 메모리 컨트롤러들을 가진다. 좁은 채널은 캐시라인 요청에 더 긴 데이터 버스트를 요구하기 때문에 DRAM 메모리 컨트롤러들의 독립적 사용은 더 높은 대역폭 특성을 얻을 수 있게 한다. 결론적으로 새로운 시스템 컨트롤러들은 추가 면적등의 Cost에 불구하고 다수의 메모리 컨트롤러로 설계된다.

단일 컨트롤러, 다수의 채널 구성에는 두개의 옵션이 존재한다.

1. 서로 잘 안맞는 메모리 모듈 쌍의 사용을 허용, 메모리 컨트롤러는 Asymmetric 모드로 동작, 오직 하나의 채널에만 일시적드로 접근 가능, 이 구성에서의 최대 시스템 대역폭은 단일 피지컬 채널의 대역폭과 동일하다.

2. 특정한 열의 접근 명령만 있으면 여러 열의 데이터를 한번에 읽을 수 있는 방식, 아래 그림은 SDRAM 메모리 시스템에서 열에 접근하는 샘플 타이밍 다이어 그램을 보여준다. 이는 오늘날의 동기화 DRAM 디바이스가 개발되기전까지 지속되었따.

10.2.2 랭크

위 그름은 DRAM 메모리 시스템에서 DRAM 디바이스의 2개의 랭크로 된 구성을 보여준다. 이전의 DRAM 메모리 시스템에서 어드레스와 명령 버스들은 메모리 시스템의 모든 DRAM 디바이스에 연결되어있다고 그려졌다. 그러나 큰 폭의 데이터 버스는 분할되고 서로 다른 DRAM 디바이스에 연결된다.

오늘날 메모리 시스템에서는 다수의 DRAM 디바이스들은 주어진 메모리 시스템에서 요구되는 데이터 버스 폭을 공급하기 위해서 같이 묶이게 된다. 예를들어 하나의 메모리 랭크에서는 72bit 너비의 데이터 버스를 형성하기 위해서 각각 4bit 너비의 데이터 버스들을 가진 18개의 DRAM 디바이스들이 필요하다. 즉 18개의 DRAM 디바이스들의 묶음을 랭크라고 칭한다.

10.2.3 뱅크

이전장(아직 공부안함)에 기술한 것과 같이 뱅크라는 단어는 DRAM 디바이스, 명령에 대하여 함께 작동하는 DRAM 디바이스 묶음, DRAM 메모리의 서로다른 피지컬 채널들 내에서 독립적인 메모리 배열들의 묶음을 의미한다.

이 절에서 뱅크는 오직 DRAM 디바이스 내에서 독립적인 메모리 배열들의 묶음을 표현하는데 사용한다.

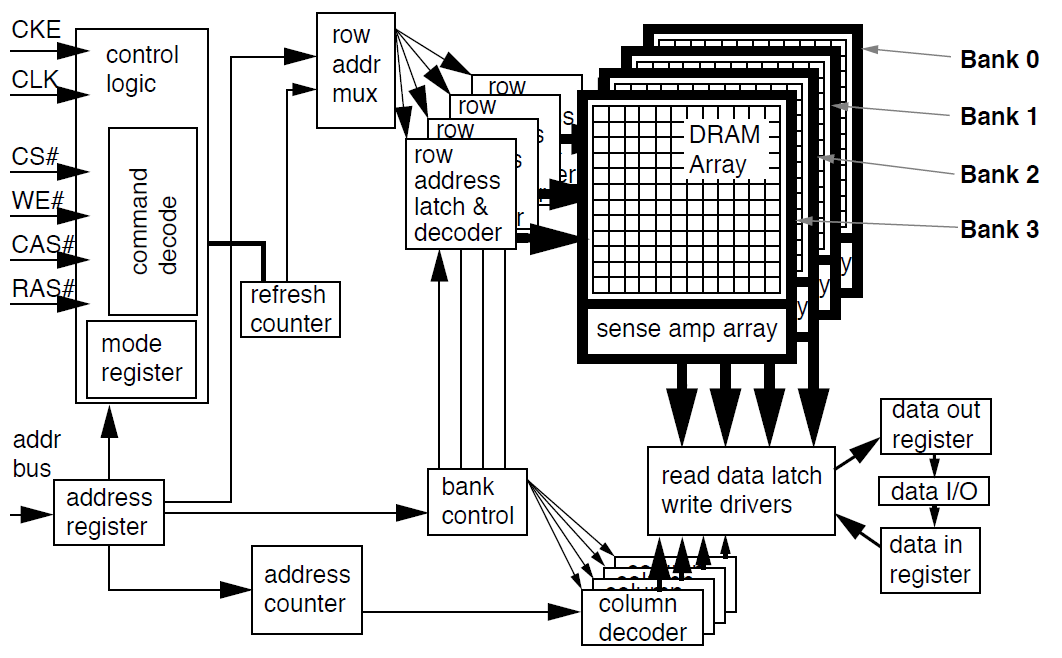

아래 그림은 DRAM 배열들로 이루어진 4개의 뱅크를 가진 SDRAM 디바이스를 보여주고 있다. 오늘날의 DRAM 디바이스는 다른 DRAM 배열들에 대하여 여러 독립적인 접근이 병렬적으로 행해질 수 있도록 여러개의 뱅크들로 구성된다.

각 뱅크들은 행에 대한 접근 사이클에서 다른 위상에 존재할 수 있는 독립적인 배열이다. 따라서 어떤 DRAM 디바이스에서 여러 뱅크들은 각기 독립적으로 활성화 될 수 있으며, 이는 DRAM 디바이스의 전력 소모 졔약에 의존하게 된다.

10.2.4 로우

DRAM 디바이스에서 로우란 활성화 명령에 응답하여 병렬적으로 활성화되는 셀들의 그룹을 칭한다.

종래의 시스템 토폴로지를 사용하는 DRAM 메모리 시스템에서는 여러 DRAM 디바이스들이 일반적으로 일정 메모리 랭크에 병렬적으로 연결되어 있다.

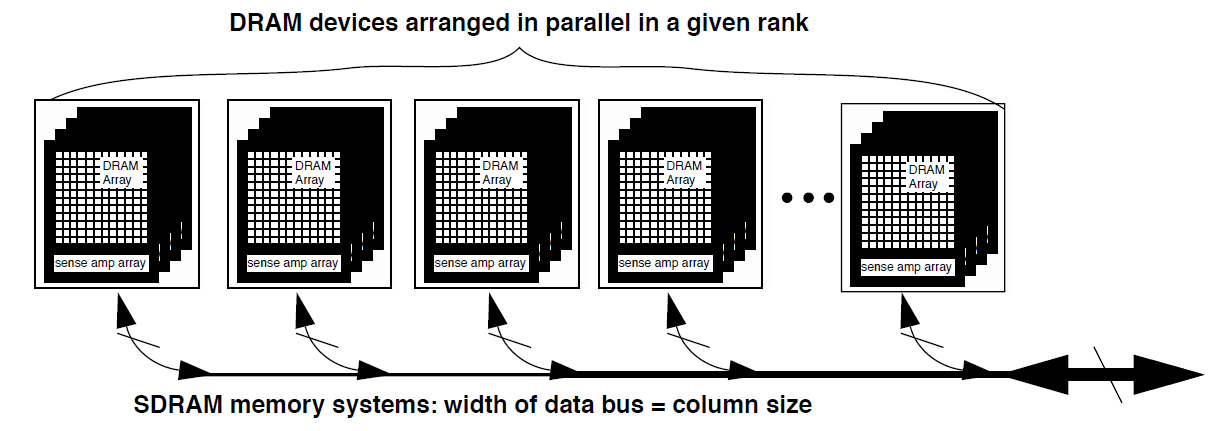

아래의 그림은 DRAM 디바이스들이 어떠한 방식으로 병렬적으로 연결되어 메모리의 랭크를 형성하는지 보여준다.

랭크로서 연결된 DRAM 디바이스들의 효과는 로우 활성화 명령이 특정 메모리 랭크에서 모든 DRAM 디바이스들의 같은 어드레스를 가진 로우를 확성화 시키는 것이다. 메모리 컨트롤러 관점에서 이러한 배열은 로우의 크기가 단순하게 특정 랭크에 있는 DRAM 디바이스들의 수를 특정 DRAM 디바이스의 로우의 크기에 곱한 값을 의미하며, DRAM 로우는 특정 메모리 랭크의 여러 DRAM 디바이스들에 걸쳐있다.

Pre-charge 명령이 메모리 컨트롤러에 의해 나오기 전까지 로우 활성화 명령이 본질적으로 sense amplifier에서의 메모리 페이지를 저장하고 있기 때문에 로우라는 것은 DRAM Page 라고도 불린다.

10.2.5 칼럼

DRAM 메모리 시스템에서 칼럼은 메모리의 자체 어드레스를 가진 가장 작은 단위이다. 아래의 그림은 랭크에서 설명한 그림과 유사한 토폴로지를 가지는 SDRAM과 같은 메모리 시스템에서의 데이터 칼럼의 크기는 데이터 버스의 폭과 같다는 것을 보여준다.

'책 > 메모리 시스템' 카테고리의 다른 글

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-1' (0) | 2021.10.28 |

|---|---|

| 메모리 시스템 Ch10_'DRAM 메모리 시스템 구조-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch9_'DRAM 시스템 시그널링 및 타이밍-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch9_'DRAM 시스템 시그널링 및 타이밍-1' (0) | 2021.10.28 |

| 메모리 시스템 Ch8_'DRAM 디바이스 조직 : 기본 회로와 구조-4' (0) | 2021.10.28 |