DRAM 메모리-액세스 프로토콜은 범용적으로 사용되는 프로토콜로 DRAM 메모리 컨트롤러가 디바이스와 주고받는 데이터를 통제하기위한 커맨다와 타이밍 제약에 대하여 정의하고 있다. 기본적으로 DRAM 커맨드들과 이 커맨드들을 수행하면서 발생하는 이벤트들의 순서에 초점을 두고 DRAM 메모리-액세스 프로토콜에 대해 알아보도록한다. Direct DRAM, GDDRx, FCRAM과 같은 전문적, 고성능 DRAM은 기술되어있듯 미세하게 다른 커맨드, 타이밍과 상호작용을 가진다.

11.1 기본적인 DRAM 커맨드

오늘날의 DRAM 시스템들의 커맨드들 조합의 수가 증가하면서 해당 프로토콜에 대한 자세한 검토는 어렵고 복잡하다. 다행히 제한된 수의 기본적인 커맨드를 가지고 메모리-액세스 프로토콜을 모델링 할 수 있다. 해당 절에서는 5개의 기본 커맨드를 다룬다.

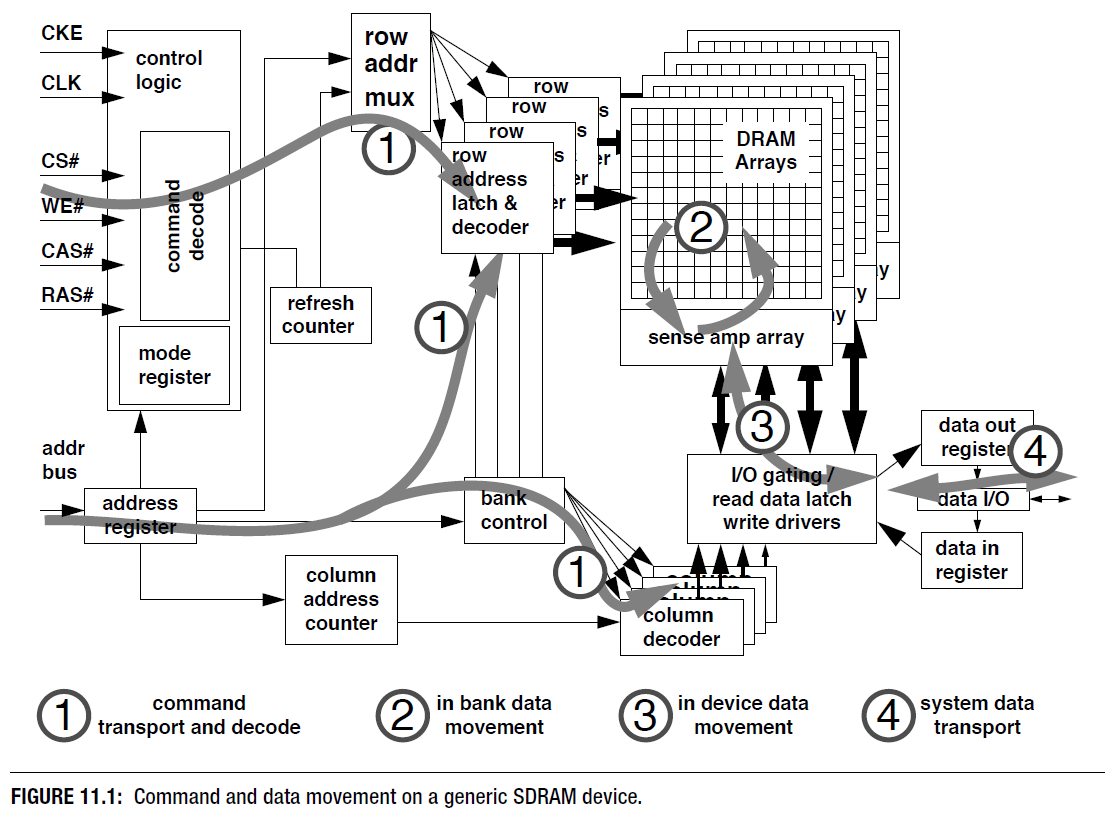

그림 11.1은 일반적인 DRAM 디바이스의 예시이다. 설명하는 DRAM 메모리-액세스 프로토콜은 자원 이용 모델을 기반으로 한다.

자원 이용 모델은 두개의 다른 커맨드들이 정해진 시간 내에 동일한 자원을 사용하지 않는 한도 내에서 완벽히 파이프라인 될 수 있다.

그림 11.1은 DRAM 커맨드를 위한 네 가지 중복된 동작 상태를 대략적으로 설명하고 있다.

1번 상태에서는 커맨드 신호가 어드레스와 커맨드 버스들을 통해서 전송되고 DRAM 디바이스에서 디코딩된다.

2번 상태에서는 뱅크에 있는 데이터가 셀에서 sense amplifier로 이동하거나, sense amplifier에서 다시 DRAM 어레이들로 이동한다.

3번 상태에서는 데이터가 공용 I/O 게이팅 회로로 이동하고 다시 read latches wirte driver로 상황에 맞게 이동한다.

4번 상태에서는 칼럼 read 커맨드 상태의 DRAM디바이스 또는 칼럼 write 커맨드 상태의 메모리 컨트롤러에 의해 read 데이터가 데이터 버스를 통해 전송된다.

데이터 버스가 다수의 랭크에 연결되는 상황을 막기위해, 두개의 서로다른 랭크로 향하는 커맨드가 동시에 공용 데이터 버스를 사용할 수 없다.

추가적으로 해당 프로토콜은 커맨드 조합사이의 타이밍 조건을 정의한다.

11.1.1 일반적인 DRAM 커맨드 포맷

그림 11.2는 일반 DRAM 커맨드 진행을 보여준다. tCMD는 DRAM 컨트롤러로 부터 DRAM 디바이스까지 커맨드를 전송하는 데 걸리는 시간이다. tPARAMETER1은 일반적인 '2번 상태'의 지속시간을 나타내는 타이밍 변수이다. tPARAMETER2는 커맨드가 동일한 디바이스 내부의 DRAM 어레이를 다수의 뱅크들이 공용으로 사용하는 자원을 사용한 시간을 나타낸다. 즉 tPARAMETER1은 DRAM 어레이의 정해진 뱅크 내부의 공유자원에 의해 제한되는 상황에서 두개의 커맨드를 스케쥴링 하는데 필요한 최소한의 시간 간격이다. tPARAMETER2는 DRAM 어레이들의 다수의 뱅크들이 공용으로 사용하는 자원에 의해 제한되는 상황에서 두개의 커맨드를 스케줄링하는데 필요한 최소한의 시간간격을 나타낸다.

11.1.2 타이밍 파라미터들의 요약

tAL : Posted CAS 커맨드를 위해 DDRx SDRAM 디바이스에서 사용되는 Column Access에 Latency

tBURST : Data Busrt 지속시간. 데이터 버스의 데이터 버스트가 차지하는 시간이다. 일반적으로 4~8 beats 데이터, DDR SDRAM에서는 4 beats의 데이터가 2회의 Full clock cycles를 차지한다.

tCAS : Column Access Strobe Latency. DRAM 디바이스에 의한 Column 액세스 커맨드와 데이터 반환 시작 사이의 시간 간격. tCL 이라고도 한다.

tCCD : 내부 Burst(Prefetch) 길이에 따라 결정되는 최소 Column 커맨드 타이밍. Column Read를 위해 내부 버스트를 여러번 사용하여 더 긴 버스트를 생성한다.

tCMD : 커맨드 전송 시간. DRAM 컨트롤러에서 DRAM 디바이스로 전송될 때 버스에서 커맨드가 차지하는 시간이다.

tCWD : DRAM 컨트롤러에 의한 데이터 버스에서의 Column-Write 커맨드와 데이터 Placement 사이의 시간 간격이다.

tFAW : 4개(Row) Bank Activation Window. 최대 4개 Bank가 작동할 수 있는 time-frame이다. Bank가 4개 이상인 DDR2, DDR3 디바이스에서 최대 전류 프로파일을 제한한다.

tOST : ODT 스위칭 시간. ODT 제어를 Rank에서 Rank로 전환하는 시간 간격이다.

tRAS : Row Access Strobe. Row Access 커맨드와 DRAM 어레이의 Data Restore사이의 시간 간격이다. DRAM Bank는 이전 Bank Activate후 최소 tRAS 시간까지는 Precharge 할 수 없다.

tRC : Row Cycle. Bank의 다른 Row에 대한 Access 사이의 시간 간격이다. tRC = tRAS + tRP

tRCD : Row에서 Column 커맨드 지연. Row 액세스와 Sense Amplifier에서의 Data Ready 사이 시간 간격이다.

tRFC : Refresh Cycle Time. Refresh와 Activation 커맨드사이의 시간 간격이다.

tRP : Row Precharge. 다른 Row 액세스를 위해 DRAM 어레이가 Precharge 하는데 걸리는 시간 간격이다.

tRRD : Row Activate에서 Row Activate 사이의 간격. 동일한 DRAM 디바이스에 대한 두 개의 Row Activate 커맨드 사이의 최소 시간 간격이다. 최대 전류 프로파일을 제한한다.

tRTP : Read to Precharge 사이 간격. Read와 Precharge 커맨드 사이의 시간 간격이다.

tRTRS : Rank와 Rank 전환 시간 간격. DDR, DDR2 SDRAM에서 사용된다. SDRAM, Direct TDRAM에서는 사용되지 않는다. DDR SDRAM에서 한번의 Full Cycle

tWR : Write 복구 시간. Write 데이터 버스트 종료와 Precharge 커맨드 시작사이의 최소 시간 간격이다. Sense Amplifier가 데이터를 Cell로 복원 한다.

tWTR : Write 지연 시간. Write 데이터 버스트 종료와 Column Read 커맨드 시작사이의 최소 시간 간격이다. Read 커맨드가 시작되기전에 I/O 게이팅이 Sense Amplifier를 Overdrive 할 수 있다.

'책 > 메모리 시스템' 카테고리의 다른 글

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-3' (0) | 2021.10.28 |

|---|---|

| 메모리 시스템 Ch11_'기본적인 DRAM 메모리 액세스 프로토콜-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch10_'DRAM 메모리 시스템 구조-2' (0) | 2021.10.28 |

| 메모리 시스템 Ch10_'DRAM 메모리 시스템 구조-1' (0) | 2021.10.28 |

| 메모리 시스템 Ch9_'DRAM 시스템 시그널링 및 타이밍-2' (0) | 2021.10.28 |