DMA의 정의

DMA는 특정한 HW 시스템(Hard-disk, GPU 등)이 CPU와 독립적으로 주 시스템 메모리(RAM)에 Access 할 수 있도록 하는 컴퓨티 시스템의 기능이다.

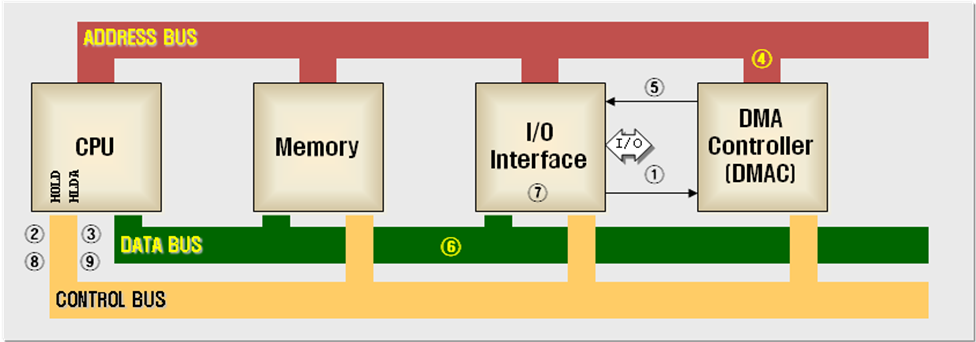

CPU는 상태, 제어정보만을 교환하고 직접적인 데이터 전송은 DMA Controller가 버스를 제어하고 I/O와 메모리간에 교환한다.

등장 배경

DMA와 반대되는 개념으로 PIO(Programed Input/Output)이 존재한다. HW 시스템들 사이에 전송되는 모든 데이터가 CPU를 거쳐가는 방식이다. PIO를 보완하기위해 인터럽트, DMA등이 고안되었다.

인터럽트 방식은 PIO방식보다는 효율적이지만 I/O를 위한 상태, 제어정보, 데이터 전송을 위해 CPU의 많은 개입이 필요하기 때문에 오버헤드가 발생한다.

최근 고속의 I/O 장치들은 인터럽트로인해 CPU time의 직접적인 감소

DMA 특징

1. CPU의 개입없이 독립적으로 HW 시스템, 메모리 사이의 데이터 직접 전송

2. I/O를 위한 인터럽트 발생 횟수를 최소화해 CPU Stall을 최소화

3. DMA Controller와 CPU는 시스템 버스를 공유한다.

PIO(Programed I/O) : Port를 이용한 데이터 전송, 프로그램에 의해 제어, I/O 완료될때 까지 CPU Stall된다.

Interrupt Driven I/O : I/O 인터페이스가 HW 장치에 Status를 요청, Ready Status 일때 인터럽트가 구동되어 CPU에 I/O 요청한다. 따라서, Context Switching 과정을 통해 인터럽트 서비스 루틴을 수행한다.

DMA : CPU의 큰 개입없이 I/O 장치와 Memory 사이의 데이터 전송을 담당하는 Controller를 사용한다. 따라서 시스템 버스에 Controller 모듈이 추가된다. 해당 모듈은 한번에 1 Word씩 모든 데이터 블록을 전송한다. 전송이 시작되거나 완료되면 CPU에게 인터럽트 구동

Channel I/O : DMA 개념을 확장, I/O만을 위한 전용 처리 장치, CPU처럼 독자적으로 메모리에 저장된 명령어를 처리할 수 있다. I/O Channel은 CPU의 개입없이 I/O를 수행한다.

동작 방식

1. I/O 인터페이스가 DMA Controller에게 DMA 서비스를 요청

2. CPU의 HOLD Pin에 Request가 전송되어 시스템 버스에 대한 제어를 DMA가 획득 (Active High)

3. CPU의 HLDA(Hold Acknowledge) Pin으로부터 DMAC에 Bus grant가 리턴됨 (Active High)

4. DMAC는 Address bus에 Address Register의 Contents를 적재한다

5. DMAC는 I/O Interface에게 데이터를 데이터버스에 적재하도록 DMA Acknowledgement를 전송한다

6. Data Byte가 Address Bus에 의해 식별된 메모리 위치로 전송된다.

7. I/O Interface는 데이터를 지속적으로 전송유지 한다 (Latch)

8. Bus Request 가 Drop되어 HOLD가 Low 상태가 되어 DMAC는 Bus에 대한 사용권을 돌려준다.

9. BUS Grant가 Drop되어 HLDA가 Low 상태가 된다

10. 이후, Address Register가 1 증가되고, Byte Count는 1 감소된다

11. Byte Count가 0이 아니면 Step 1로, 0이면 정지

'개인 공부 > 메모리' 카테고리의 다른 글

| SPEC2006 워크로드별 특성 - 1 (0) | 2022.01.06 |

|---|---|

| Memory Controller Policy (0) | 2021.06.10 |

| MSHRs(Miss Status Holding Register) (1) | 2021.06.10 |

| DRAM Operation, Memory Control & Memory Latency - 3 (2) | 2021.06.08 |

| DRAM Operation, Memory Control & Memory Latency - 2 (0) | 2021.06.07 |