A 192-Gb 12-High 896-GB/s HBM3 DRAM with a TSV Auto Calibration Scheme and Machine-Learning-Based Layout Optimization

HBM3 Architecture

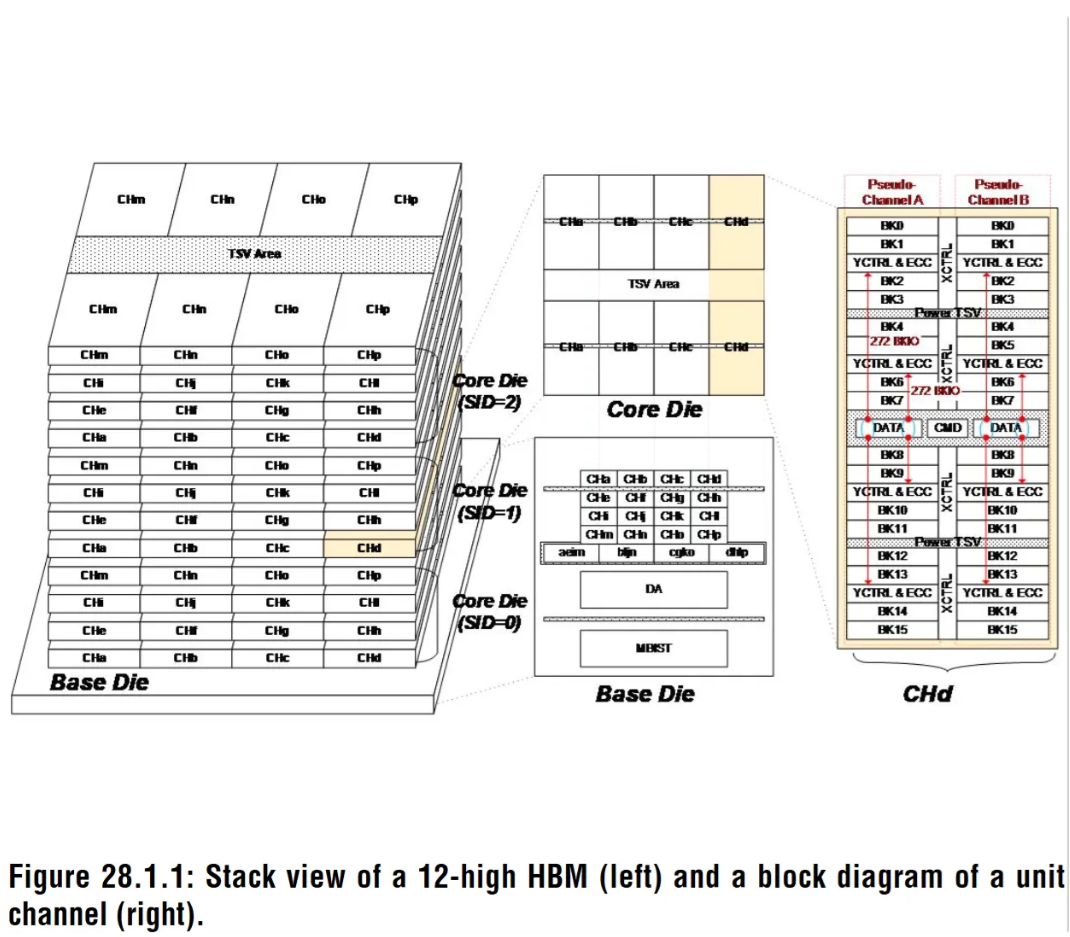

제안된 HBM3 DRAM의 적층 다이어그램은 그림 28.1.1에 나와 있습니다. HBM3 DRAM은 최대 12단 적층과 16개의 독립 채널을 지원하여, 8단 적층과 8개 독립 채널로 제한되었던 이전 HBM2E DRAM에 비해 더 높은 밀도와 향상된 병렬성을 지원합니다. 제안된 아키텍처는 코어 다이에 4개의 채널을 포함하며, 4개의 슬라이스가 단일 단위 랭크를 형성하고 12개의 슬라이스가 3개의 랭크에 해당합니다. 코어 다이는 베이스 다이 위에 수직으로 적층되고 TSV를 통해 연결됩니다.

각 채널은 2개의 의사-채널로 세분화되며, 각 의사-채널은 4개의 뱅크 그룹에 16개의 뱅크로 구성됩니다. 뱅크당 160Mb의 밀도를 가지며, 여기에는 시스템 수준의 신뢰성 검사를 위한 16Mb의 ECC 패리티와 8Mb의 메타데이터(MD)가 포함됩니다.

주요 기술

온다이 ECC (On-Die ECC): 셀 오류로 인한 DRAM 오작동을 줄이기 위해 심볼 기반의 온다이(OD) ECC가 사용됩니다. 그림 28.1.2는 셀 어레이 구성과 제안된 ECC 방식을 보여줍니다. 다중 비트 오류를 복구하기 위해, 제안된 OD ECC 엔진에는 (19, 17) 단일 심볼 오류 정정 리드-솔로몬 코드가 구현되었습니다. 쓰기 작업 중에는 17개의 (DQ+MD) 심볼에 의해 2개의 패리티 심볼이 생성됩니다.

머신러닝 기반 레이아웃 최적화: 모든 DQ 신호를 완벽하게 정렬하는 것은 어렵습니다. 각 I/O의 라인 부하를 균일하게 설계할 수 없기 때문입니다. 이러한 문제를 완화하기 위해, PHY에서 TSV DWORD에 이르는 전역 내부 I/O 버스에 대해 향상된 설계 방법론이 제안되었습니다 (그림 28.1.4). Q-러닝 알고리즘에 기반한 머신러닝 기법이 전역 라인 설계를 최적화하기 위해 적용되었으며 , 각 드라이버의 최적 크기를 결정하기 위해 유전 알고리즘이 사용되었습니다. 그 결과, 제안된 설계 방법론은 읽기 및 쓰기 작업 모두에서 그룹 신호 스큐를 각각 최대 33%와 19%까지 줄일 수 있었습니다.

TSV 랭크-투-랭크 자동 보정: 서로 다른 공정의 코어 슬라이스가 함께 적층될 때, 랭크 간 읽기 작업 중 각 슬라이스 간의 CLK-to-output 지연 차이로 인해 속도가 저하될 수 있습니다. 그림 28.1.5는 제한된 영역에 물리적으로 적합하고 작동 시간이 짧은, 제안된 TSV 랭크-투-랭크 보정 회로를 보여줍니다. 이 회로는 TDC(Time-to-Digital Converter)를 사용하여 다중 랭크 간의 스큐 차이를 동시에 계산하고, 그 결과 코드를 레지스터에 저장하여 모든 TSV I/O 회로 영역으로 인코딩된 차이 값을 보냅니다.

저전력 설계: HBM3 DRAM은 최대 12개 슬라이스의 적층 다이 구조를 기반으로 하므로, 열 문제를 완화하기 위해 저전력 설계가 필수적입니다. 전력 소모를 관리하기 위해 외부 I/O 인터페이스에 0.4V(VDDDOL)의 저전압 전원 공급 장치가 적용됩니다. PHY에서 TSV 연결을 담당하는 내부 I/O 인터페이스에도 이 VDDDOL 전원이 사용됩니다.

측정된 슈무(shmoo) 그래프는 그림 28.1.6(왼쪽)에 나와 있습니다. 결과는 12단으로 적층된 제작된 HBM3 DRAM이 1.0V 작동 전압에서 핀당 7.0Gb/s의 데이터 속도를 달성함을 확인시켜 주며, 이는 16채널 작동 기준으로 896GB/s의 대역폭에 해당합니다. HBM2E DRAM과의 주요 특징 비교는 그림 28.1.6(오른쪽)에 나타나 있습니다. 요약하면, 제안된 HBM3 DRAM 칩은 공급 전압을 0.91배 줄이면서 1.75배의 피크 대역폭을 달성했습니다.

'개인 공부 > DRAM' 카테고리의 다른 글

| High Bandwidth Memory 2 (HBM2) (3) | 2025.08.06 |

|---|---|

| High Bandwidth Memory (HBM) (2) | 2025.08.05 |

| DDR, LPDDR, GDDR, HBM (2) | 2025.08.05 |

| DRAM (Dynamic Random Access Memory) (4) | 2025.08.05 |