4.1 서론

프로세서를 구현하는 데 사용하는 원리와 기법들에 대한 설명

LEGv8 명령어 집합 핵심 부분의 구현을 설계

LDUR(lw), STUR(sw), ADD, SUB, AND, ORR, CBZ, B

모든 명령어의 첫 두단계는 다음과 같이 동일하다.

1. 프로그램 카운터(PC)를 프로그램이 저장되어 있는 메모리에 보내어 메모리로부터 명령어를 가져온다.

2. 읽은 레지스터를 선택하는 명령어 필드를 사용하여 하나 또는 두 개의 레지스터를 읽는다. LDUR, CBZ 명령어는 하나만 읽으면 되지만 대부분의 다른 명령어는 레지스터 두 개를 읽는다.

PC -> Instruction Memory, Fetch Instruction

Register Numbers -> Register File, Read Registers

Depending on Instruction Class

Use ALU to calculate

Arithmetic result, Memory address for load/store, Branch target address

Access data memory for load/store

PC <- target address or PC + 4

선이 교차하는 곳 즉, PC에 들어갈 두 가산기, 레지스터 파일로 들어갈 ALU 출력 및 Ddata Memory 출력, 레지스터나 명령어의 수치 필드에 의해 종속된 ALU의 두번째 입력 부분들은 멀티플렉서(MUX)라 불리는 소자를 사용해 구성된다.

어떠한 유닛들은 명령어 종류에 따라 다르게 제어되어야한다. 하지만 이러한 부분이 빠져있다.

예를들어 Data Memory는 Load 일때 읽기, Store일때 쓰기를 해야한다. 레지스터 파일은 Load, 산술/논리 때 쓰기 한다.

Control Unit은 기능 유닛들과 두 멀티플렉서의 제어선 값을 결정하는데 사용하는 것으로, 명령어를 입력으로 한다.

상단의 MUX는 PC+4와 분기 목적지 주소중 결정하는 것인데, ALU의 Zero 출력으로 제어된다.

중단의 MUX는 ALU 출력과 Data Memory 출력중에서 어느 것을 레지스터 파일에 출력하는지 결정한다

하단의 MUX는 ALU의 두번째 입력을 레지스터에서 받을것인지, 명령어 변위 필드에서 받을 것인지 결정한다.

4.2 논리 설계 관례

두가지 소자

조합소자 : 데이터값에만 동작하는 소자, 같은 입력이 주어지면 항상 같은 출력을 낸다 (ALU)

상태소자 : 소자 내부에 기억장소가 존재,두 개의입력(데이터,클럭)과 한 개의 출력(이전데이터)을 가진다.

(Data Memory, Register file)

에지 구동 클럭킹(Edge-triggered clocking)

순차논리소자에 저장된 값은 클럭 에지에서만 수정 가능하다.

회로가 하나의 클럭사이클로 동작한다면, 모든신호가 상태소자 1에서 나와서 조합회로를 거쳐 상태소자2에 전달되는데 하나의 클럭 사이클이 걸린다.

4.3 데이터패스 만들기

Instruction Memory : 프로그램의 명령어를 저장하고 주소가 주어지면 해당 명령어를 보내주는 메모리 유닛

PC : Program Counter, 현재 명령어 주소를 가지고 있는 레지스터

Add : 가산기(조합회로), PC를 다음 명령어 주소로 증가시킨다.

R-Format Instructions(산술/논리 명령어)

두 개의 레지스터를 읽고 레지스터 내용에 ALU 연산을 수행하며 그 결과를 레지스터에 쓴다.

ADD, SUB, AND, ORR 명령어를 포함 ex) ADD X1, X2, X3 (X1 = X2 + X3)

프로세서의 범용레지스터 32개는 Register File(레지스터 파일)구조 속에 들어있다.

R-형식 명령어들은 4개의 입력(레지스터 번호용3개, 데이터용 1개)와 2개의 출력(모두 데이터용), 1개의 쓰기 제어신호

레지스터 번호 입력은 5bit 크기, 데이터 입, 출력은 64bit 크기

1개의 제어신호는 레지스터 파일에 쓰기를 행할때 에지 신호로 사용된다.

ALU는 64bit 입력 두개를 받아서 64bit 결과와 0인지 아닌지 나타내는 1비트 신호를 출력한다. 또한 1개의 제어신호

Load/Store Instructions

베이스 레지스터(X2)와 명령어에 포함되어있는 9비트 부호있는 변위 필드를 더하여 메모리 주소를 계산한다.

LDUR X1, [X2, offset_value], STUR X1m [X2, offset_value]

STUR 이라면 저장할 값을 레지스터 파일(X1)에서 읽어 온다.

LDUR 이라면 메모리로 부터 읽어 들인 값을 지정된 레지스터(X1)에 써야 한다.

따라서 Load/Store Instructions 에서도 위 그림의 Register, ALU가 모두 필요하다.

9비트 변위 필드 값을 64비트 부호있는 값으로 부호확장 하기 위한 유닛(Sgn Extension Unit)이 필요하다.

또한 읽고 쓸 Data Memory Unit이 필요하며 Write/Read 제어신호, 주소입력, 데이터 입력이 필요하다.

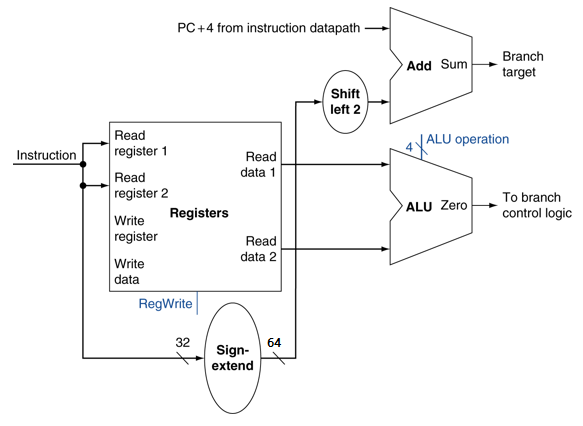

Branch Instructions

CBZ명령어는 0인지 아닌지 테스트할 레지스터 한 개와 19비트 변위의 두 피연산자를 갖는다.

ex) CBZ X1, offset

변위는 분기 명령어 주소에 대한 상대적인 분기 목적지 주소를 계산하는데 사용한다.

Branch 명령어를 구현하기 위해서는 PC값에 명령어 변위 필드의 부호확장 값을 더해 분기 목적지 주소를 계산해야한다

이후 Shift left 2를 사용해(4배) 각 명령어 들이 4bit 단위로 할당되어있는것을 맞추게 된다.

상위의 기본 명령어들 (레지스터 적재/저장, ALU연산, 분기)을 한 클럭 사이클 내에 실행 할 수 있는 Full Datapath

'책 > 컴퓨터 구조' 카테고리의 다른 글

| 컴퓨터 구조 Ch04_"The Processor-3" (0) | 2021.01.06 |

|---|---|

| 컴퓨터 구조 Ch04_"The Processor-2" (0) | 2021.01.06 |

| 컴퓨터 구조 Ch02_"Language of the Computer-2" (0) | 2020.11.19 |

| 컴퓨터 구조 Ch02_"Language of the Computer-1" (0) | 2020.11.18 |

| 컴퓨터 구조 Ch01_"Computer Abstractions and Technology" (0) | 2020.11.17 |